## Description

The CPS-1432 (80HCPS1432) is a *RapidIO Specification (Rev. 2.1)* compliant Central Packet Switch whose functionality is central to routing packets for distribution among DSPs, processors, FPGAs, other switches, or any other RapidIO-based devices. It can also be used in RapidIO backplane switching. The CPS-1432 supports Serial RapidIO (S-RIO) packet switching (unicast, multicast, and an optional broadcast) from any of its 14 input ports to any of its 14 output ports.

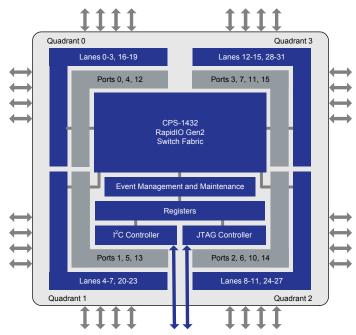

## **Block Diagram**

## **Typical Applications**

- High-performance computing

- Wireless

- Defense and aerospace

- · Video and imaging

## Features

- RapidIO ports

- 32 bidirectional S-RIO lanes

- Port widths of 1x, 2x, and 4x allow up to 20 Gbps per port

- Port speeds selectable: 6.25, 5, 3.125, 2.5, or 1.25 Gbaud

- Support Level I defined short or long haul reach, and Level II defined short-, medium-, or long-run reach for each PHY speed

- Error Management Extensions support

- Software-assisted error recovery, supporting hot swap

- I<sup>2</sup>C Interfaces

- Provides I<sup>2</sup>C port for maintenance and error reporting

- Master or Slave operation

- Master allows power-on configuration from external ROM

- Master mode configuration with external image compressing and checksum

- Switch

- 160 Gbps peak throughput

- Non-blocking data flow architecture

- Configurable for Cut-Through or Store-and-Forward data flow

- Very low latency for all packet lengths and load conditions

- Internal queuing buffer and retransmit buffer

- Standard transmitter- or receiver-controlled flow control

- Global routing or Local Port routing capability

- Supports up to 40 simultaneous multicast masks, with broadcast

- Performance monitoring counters for performance and diagnostics analysis. Per input port and output port counters

- SerDes

- Transmitter pre-emphasis and drive strength + receiver equalization provides best possible signal integrity

- Embedded PRBS generation and detection with programmable polynomials support Bit Error Rate testing

- Additional Information

- Packet Trace/Mirror. Each input port can copy all incoming packets matching user-defined criteria to a "trace" output port.

- Packet Filter. Each input port can filter (drop) all incoming packets matching user-defined criteria.

- Device configurable through any of S-RIO ports, I<sup>2</sup>C, or JTAG

- Full JTAG Boundary Scan Support (IEEE1149.1 and 1149.6)

- Lidless 784-FCBGA Package: 25 X 25 mm, 1.0 mm ball pitch

## RENESAS

# **Table of Contents**

| 1.         | About This Document                                                 |    |

|------------|---------------------------------------------------------------------|----|

|            | Additional Resources                                                |    |

|            | Document Conventions and Definitions                                |    |

|            | Revision History                                                    |    |

| 2.         | Device Description                                                  |    |

|            | Specification Compliancy                                            | 7  |

| 3.         | Functional Overview                                                 |    |

| 4.         | Interface Overview                                                  |    |

|            | S-RIO Ports                                                         |    |

|            | I2C Bus                                                             |    |

|            | JTAG TAP Port                                                       |    |

|            | Interrupt (IRQ_N)                                                   |    |

|            | Reset (RST_N)<br>Clock (REF_CLK_P/N)                                |    |

|            | Rext (REXT_N/P)                                                     |    |

|            | Speed Select (SPD[2:0])                                             |    |

|            | Quadrant Config (QCFG[7:0])                                         |    |

|            | Frequency Select (FSEL[1:0])                                        |    |

|            | Multicast (MCAST)                                                   |    |

| 5.         | Configuration Pins                                                  | 10 |

|            | Speed Select Pins SPD[2:0]                                          |    |

|            | Quadrant Configuration Pins QCFG[7:0]                               |    |

| <b>6</b> . | Absolute Maximum Ratings                                            |    |

| 7.         | Recommended Operating Conditions                                    |    |

| 8.         | AC Test Conditions                                                  |    |

| 9.         | Power Consumption                                                   |    |

| 10.        | I <sup>2</sup> C Bus                                                |    |

|            | I <sup>2</sup> C Master Mode and Slave Mode                         |    |

|            | I <sup>2</sup> C Device Address                                     |    |

|            | Signaling                                                           |    |

|            | Read/Write Figures<br>I <sup>2</sup> C DC Electrical Specifications |    |

|            | $I^2C$ AC Electrical Specifications                                 |    |

|            | I <sup>2</sup> C Timing Waveforms                                   |    |

| 11.        |                                                                     |    |

| 12.        | Configuration (Static) Pin Specification                            |    |

|            | S-RIO Ports                                                         |    |

|            | Overview                                                            |    |

|            | Definition of Amplitude and Swing                                   |    |

|            | 1.25, 2.5, and 3.125 Gbaud LP-Serial Links                          |    |

|            | Level I Electrical Specification                                    |    |

|            | 5 and 6.25 Gbaud LP-Serial Links                                    |    |

|            | Level II Electrical Specifications                                  |    |

## RENESAS

| 14. | Reference Clock                                           |  |

|-----|-----------------------------------------------------------|--|

| 15. | Reset (RST_N) Specification                               |  |

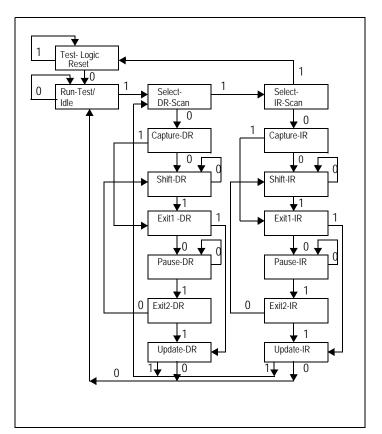

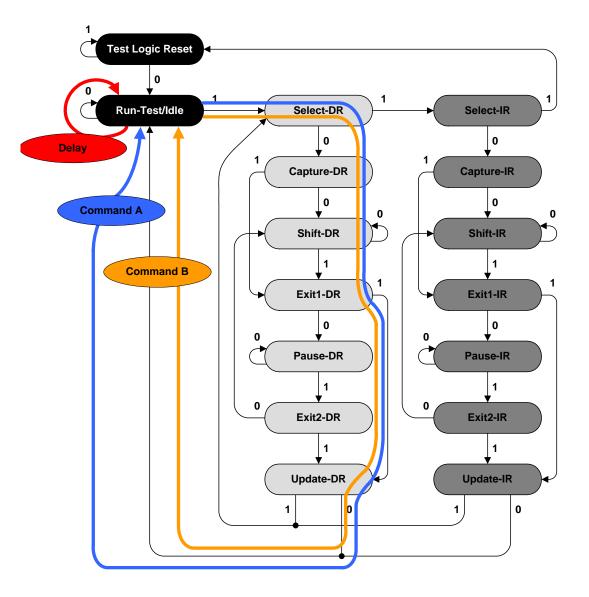

|     | JTAG Interface                                            |  |

|     | Description                                               |  |

|     | IEEE 1149.1 (JTAG) and IEEE 1149.6 (AC Extest) Compliance |  |

|     | System Logic TAP Controller Overview                      |  |

|     | Signal Definitions                                        |  |

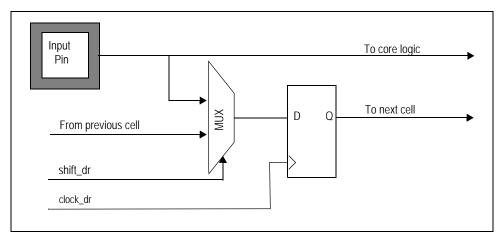

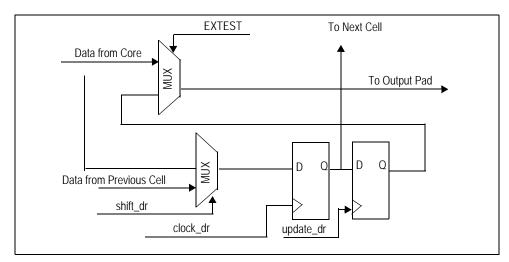

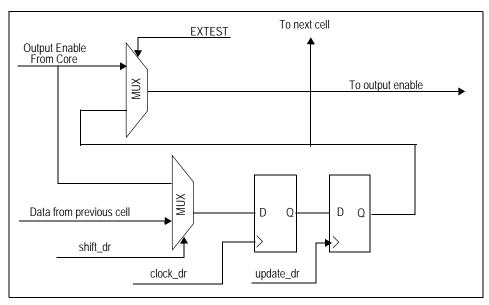

|     | Test Data Register (DR)                                   |  |

|     | Boundary Scan Registers                                   |  |

|     | Instruction Register (IR)                                 |  |

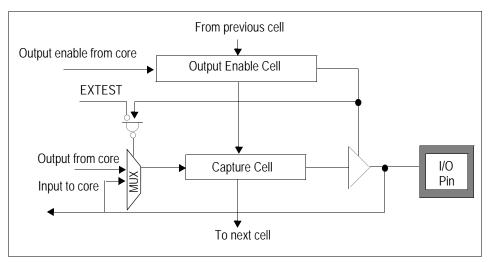

|     | EXTEST                                                    |  |

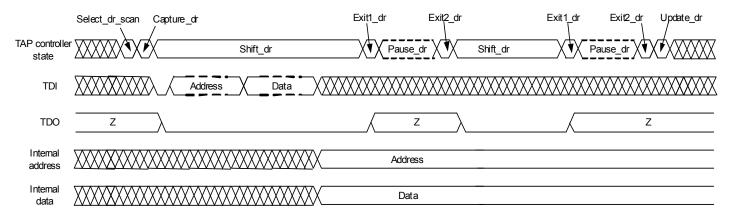

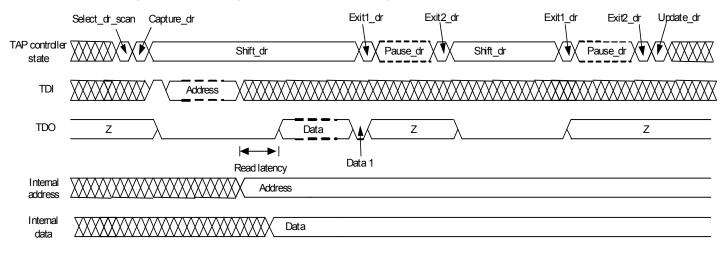

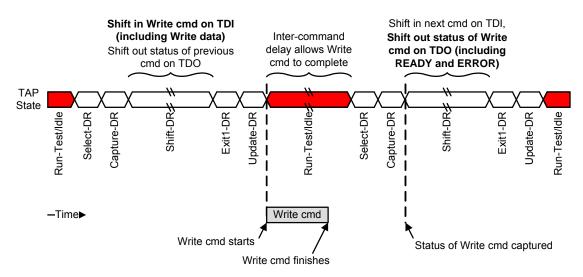

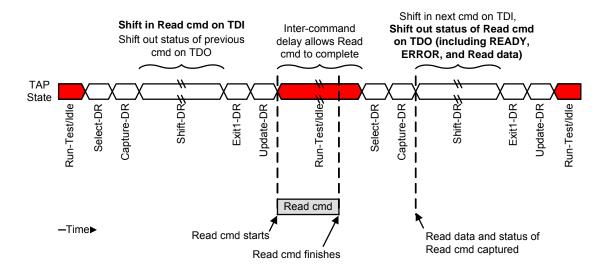

|     | Configuration Register Access (Revision A/B)              |  |

|     | Configuration Register Access (Revision C)                |  |

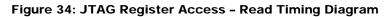

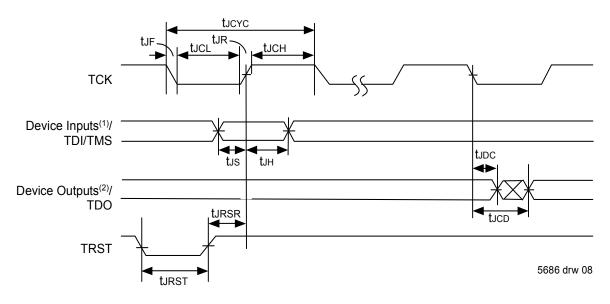

|     | JTAG DC Electrical Specifications                         |  |

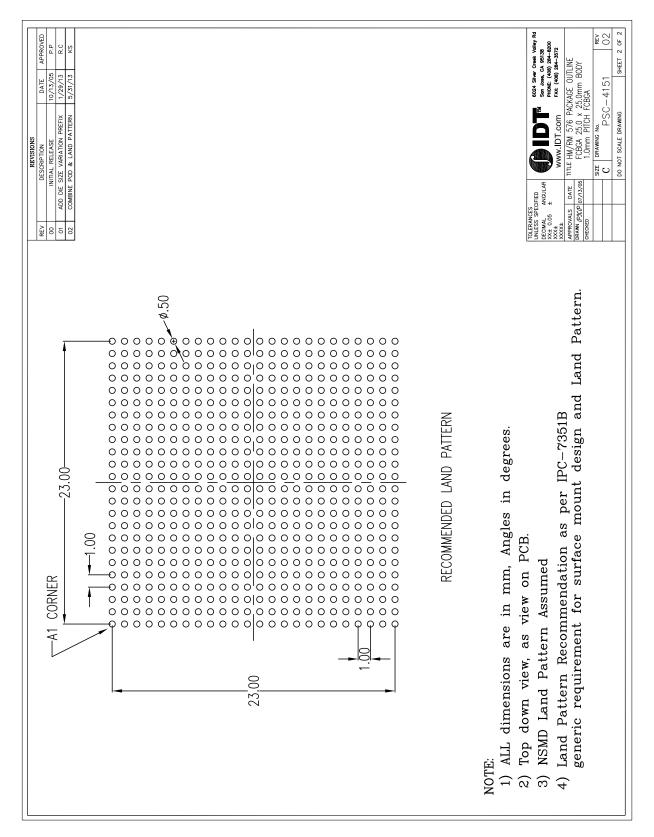

|     | JTAG AC Electrical Specifications                         |  |

|     | JTAG Timing Waveforms                                     |  |

| 17. | Pinout and Pin Listing                                    |  |

|     | Pinout — Top View                                         |  |

|     | Pin Listing                                               |  |

| 18. |                                                           |  |

| 10. | Package Physical Specifications                           |  |

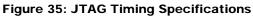

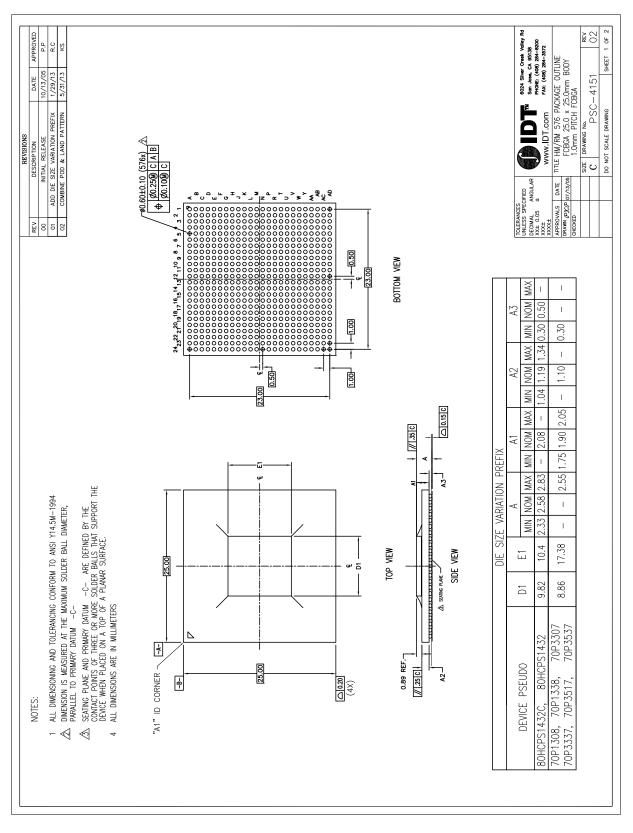

|     | Package Outline Drawings                                  |  |

|     | Thermal Characteristics                                   |  |

| 10  |                                                           |  |

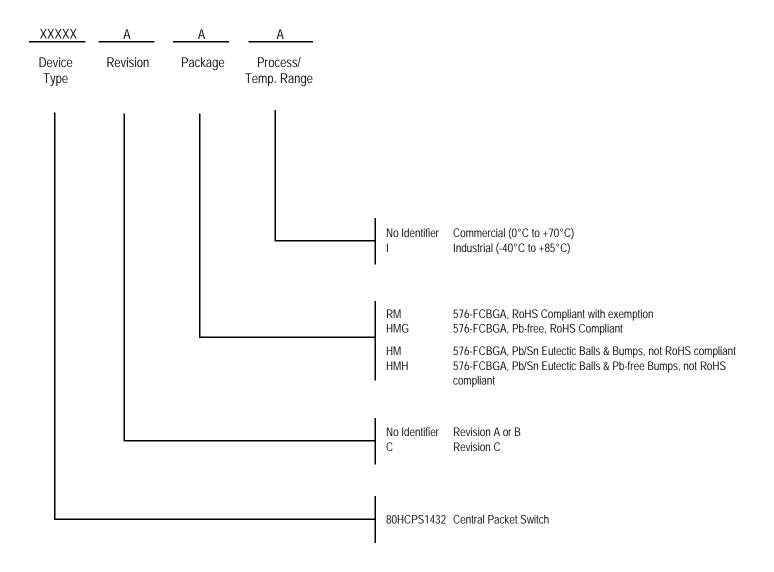

| 19. | Ordering Information                                      |  |

## 1. About This Document

### Introduction

The *CPS-1432 Datasheet* provides hardware information about the CPS-1432, such as electrical and packaging characteristics. It is intended for hardware engineers who are designing system interconnect applications with the device.

### **Additional Resources**

The *CPS-1432 User Manual* describes the functionality and configuration capabilities of the device. In addition, there are many other resources available that support the CPS-1432. For more information, please contact IDT for support.

## **Document Conventions and Definitions**

This document uses the following conventions and definitions:

- · To indicate signal states:

- Differential signals use the suffix "\_P" to indicate the positive half of a differential pair.

- Differential signals use the suffix "\_N" to indicate the negative half of a differential pair.

- Non-differential signals use the suffix "\_N" to indicate an active-low state.

- To define buses, the most significant bit (MSB) is on the left and least significant bit (LSB) is on the right. No leading zeros are included.

- To represent numerical values, either decimal, binary, or hexadecimal formats are used. The binary format is as follows: 0bDDD, where "D" represents either 0 or 1; the hexadecimal format is as follows: 0xDD, where "D" represents the hexadecimal digit(s); otherwise, it is decimal.

- Unless otherwise denoted, a byte refers to an 8-bit quantity; a word refers to a 32-bit quantity, and a double word refers to an 8-byte (64-bit) quantity. This is in accordance with RapidIO convention.

- A bit is set when its value is 0b1. A bit is cleared when its value is 0b0.

- A read-only register, bit, or field is one that can be read but not modified.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

### **Revision History**

#### June 26, 2017

- · Updated the Package Outline Drawings; no technical changes

- · Updated the Ordering Information

#### April 4, 2016

- Added an R\_X2 symbol to Table 20

- Updated Heat Sink Requirement and Analysis

- Added HMG and HMH part numbers to Ordering Information

#### June 12, 2013

• Updated the note associated with VDD3A (pin Y20)

#### June 8, 2012

- Changed the maximum 3.3V supply requirement to 3.47V in Table 6 and note 2 below the table

- · Added two cautionary notes about lane reordering to Pin Listing

# RENESAS

#### April 2, 2012

- Added JTAG configuration register access information for Revision C in Configuration Register Access (Revision C)

- Updated the JTAG version number for Revision C

#### December 9, 2011

- · Loosened the Clock Input signal rise/fall minimum time specification

- · Added an additional note to the power sequencing requirements

## 2. Device Description

The CPS-1432 is a S-RIO-compliant performance-optimized switch. This device is ideally suited for intensive processing applications which require a multiplicity of DSPs, CPUs, and / or FPGAs working together in a cluster. Its very low latency, reliable packet-transfer, and high throughput make it ideal in embedded applications including communications, imaging, or industrial controls. A switched S-RIO architecture allows a flat topology with true peer-to-peer communications. It supports four standard RapidIO levels of priority, and can unicast, multicast, or broadcast packets to destination ports. With link rates to 6.25 Gbaud and transmitter pre-emphasis and receiver equalization, the device can provide up to 20 Gbps per port across 100 cm (40 inches) of FR4 with 2 connectors. This makes the device ideally suited for communicating across backplanes or cables.

The CPS-1432 receives packets from up to 14 ports. The CPS-1432 offers full support for switching as well as enhanced functions:

1. Switching — All packets are switched in accordance with the *RapidIO Specification (Rev. 2.1)*, with packet destination IDs (destID) determining how the packet is routed.

Four main switching options exist:

- a. Unicast: Packets are sent according to the packet's destID to a single destination port in compliance with the RapidIO Specification (Rev. 2.1).

- b. Multicast: Packets with a destID pointing to a multicast mask will multicast to all destination ports provided by the multicast mask. Multicasting is performed in compliance with the *RapidIO Specification (Rev. 2.1)*.

- c. Maintenance packets: In compliance with the *RapidIO Specification (Rev. 2.1)*, maintenance packets with hop\_count > 0 pass through the switch. Maintenance packets with hop\_count = 0 will operate on the switch.

- d. Broadcast: Each multicast mask can be configured so all output ports, including the source port, are included among the destination ports for that multicast operation. This feature is IDT-specific.

The CPS-1432 supports a peak throughput of 160 Gbps which is the line rate for 3 ports in 4x, 9 ports in 2x and 2 ports in 1x configuration, (each at 5.0 Gbaud = 6.25 Gbaud minus the S-RIO defined 8b/10b encoding), and switches dynamically in accordance with the packet headers and priorities.

- 5. Enhanced functions Enhanced features are provided for support of system debug. These features which are optional for the user consist of following functions:

- a. Packet Trace: The Packet Trace feature provides at-speed checking of the first 160 bits (header plus a portion of any payload) of every incoming packet against user-defined comparison register values. The trace feature is available on all S-RIO ports, each acting independently from one another. If the trace feature is enabled for a port, every incoming packet is checked for a match against up to four comparison registers. If a match occurs, either of two possible user-defined actions may occur:

i) Not only does the packet route normally through the switch to its appropriate destination port, but this same packet is copied to a "debug port" or "trace port." The trace port itself can be any of the standard S-RIO ports. The port used for the trace port is defined by the user through simple register configuration.

ii) The packet is dropped. If there is no match, the packets route normally through the switch with no action taken. The Packet Trace feature can be used during system bring-up and prototyping to identify specific packet types of interest to the user. It might be used in security applications, where packets must be checked for either correct or incorrect tags in either of the header or payload. Identified (match) packets are then routed to the trace port for receipt by a host processor, which can perform an intervention at the software level.

- b. Port Loopback: The CPS-1432 offers internal loopback for each port that can be used for system debug of the high-speed S-RIO ports. By enabling loopback on a port, packets sent to the port's receiver are immediately looped back at the physical layer to the transmitter bypassing the higher logical or transport layers.

- c. Broadcast: The device switching operation supports broadcast traffic (any input port to all output ports).

- d. Security functions: The aforementioned packet trace / filter capabilities allow packets matching trace criteria to be blocked at the input port. This function can, for example, allow untrusted (unknown source or destination) packets to be filtered, malicious or errant maintenance packets to be filtered, or boot packets to be identified to pass to a slave device.

The CPS-1432 can be programmed through any one or combination of S-RIO, I<sup>2</sup>C, or JTAG. Note that any S-RIO port can be used for programming. The CPS-1432 can also configure itself on power-up by reading directly from EPROM over I<sup>2</sup>C in master mode.

### **Specification Compliancy**

- RapidIO Specification (Rev. 2.1), Part 1: Input/Output Logical Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 2: Message Passing Logical Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 3: Common Transport Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 6: LP-Serial Physical Layer Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 7: System and Device Interoperability Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 8: Error Management Extensions Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 9: Flow Control Logic Layer Extensions Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Part 11: Multicast Extensions Specification, 08/2009, RTA

- RapidIO Specification (Rev. 2.1), Annex I: Software/System Bring Up Specification, 08/2009, RTA

- · IEEE Std 1149.1-2001 IEEE Standard Test Access Port and Boundary-Scan Architecture

- IEEE Std 1149.6-2003 IEEE Standard for Boundary-Scan Testing of Advanced Digital Networks

- The PC-BUS Specification (v 2.1), January 2000, Philips

## 3. Functional Overview

The CPS-1432 is optimized for line card and backplane switching. Its primary function is to switch data plane and control plane data packets using S-RIO between a set of devices that reside on the same line card. In addition, it can bridge communications between multiple on-board (or local) devices and a set of external line cards by providing long run RapidIO backplane interconnects. In this manner, for example, the device can serve as a switch between a set of RF cards and a set of RapidIO based DSPs in a wireless basestation.

The CPS-1432 supports packet switching from its 14 RapidIO ports. Packets can be unicast, multicast, or broadcast. The encoded data rate for each of the lanes are configurable to either 1.25, 2.5, 3.125, 5, or 6.25 Gbaud. The device supports lane groupings such that 1x, 2x, and 4x operation is provided, as defined in the *RapidIO Specification (Rev. 2.1)*.

The CPS-1432 supports the reception of S-RIO maintenance packets (type 8) which are directed to it (that is, a hop count of 0). The device can properly process and forward received maintenance packets with a hop count > 0 as defined in the *RapidIO Specification (Rev. 2.1)*. With the exception of maintenance packets, received packets are transmitted unmodified.

The CPS-1432 supports four priority levels plus Critical Request Flow (CRF), as defined in the *RapidIO Specification (Rev. 2.1), Part 6.* It is programmable by all of the following: S-RIO ports, I<sup>2</sup>C, and JTAG Interface.

From a switching perspective the CPS-1432 functions statically. As such, all input to output port mappings are configurable through registers. Unless register configurations are changed, the input to output mappings remains static regardless of the received data. The switching functionality does not dynamically "learn" which destIDs are tied to a port endpoint by examining S-RIO header fields and dynamically updating internal routing tables.

The CPS-1432 supports "Store and Forward" or "Cut-Through" packet forwarding (for more information, see the "Switch Fabric" chapter in the CPS-1432 User Manual).

## 4. Interface Overview

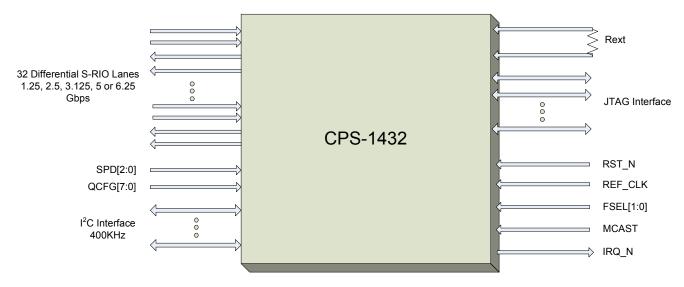

Figure 1: CPS-1432 Interfaces

### S-RIO Ports

The S-RIO ports are the main communication ports on the chip. These ports are compliant with the *RapidIO Specification (Rev. 2.1)*. For more information, see the *RapidIO Specification (Rev. 2.1)*.

The device provides up to 32 S-RIO lanes. The encoded data rate for each of the lanes is configurable to either 1.25, 2.5, 3.125, 5, or 6.25 Gbaud as defined in the *RapidIO Specification (Rev. 2.1), Part 6.*

## I<sup>2</sup>C Bus

This interface can be used instead of the standard S-RIO or JTAG ports to program the chip and to check the status of registers - including the error reporting registers. It is fully compliant with the  $I^2C$  specification, it supports master and slave modes and supports both Fast and Standard-mode buses [1]. For more information, see  $I^2C$  Bus.

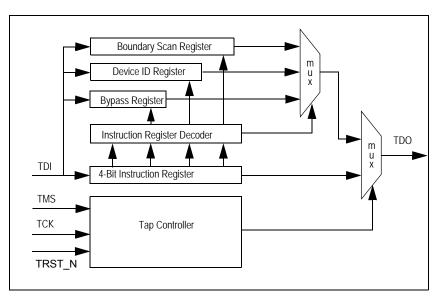

## JTAG TAP Port

This TAP interface is IEEE1149.1 (JTAG) and 1149.6 (AC Extest) compliant [11, 12]. It can be used instead of the standard S-RIO or I<sup>2</sup>C ports to program the chip and to check the status of registers - including the error reporting registers. It has 5 pins. For more information, see JTAG Interface.

### Interrupt (IRQ\_N)

An interrupt output is provided in support of Error Handling functionality. This output can flag a host processor if error conditions occur within the device. For more information, see the "Event Management" chapter in the *CPS-1432 User Manual*.

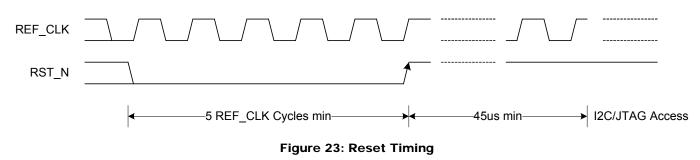

### Reset (RST\_N)

A single Reset pin is used for full reset of the CPS-1432, including setting all registers to power-up defaults. For more information, see the "Reset and Initialization" chapter in the CPS-1432 User Manual.

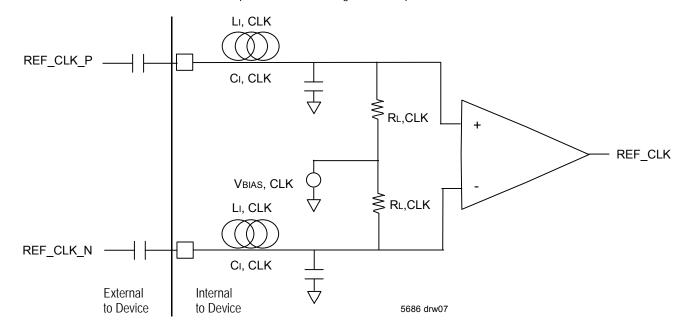

## Clock (REF\_CLK\_P/N)

The single system clock (REF\_CLK\_P/N) is a 156.25-MHz differential clock.

## RENESAS

## Rext (REXT\_N/P)

These pins establish the drive bias on the SerDes output. An external bias resistor is required. The two pins must be connected to one another with a 9.1k Ohm resistor. This provides robust SerDes stability across process and temperature.

## Speed Select (SPD[2:0])

These pins define the S-RIO port speed at RESET for all ports. SPD[2:0] can be configured as follows:

- 000 = 1.25 Gbaud

- 001 = 2.5 Gbaud

- 01X = 5 Gbaud

- 100 = Reserved

- 101 = 3.125 Gbaud

- 11X = 6.25 Gbaud

For more information, see Speed Select Pins SPD[2:0].

### Quadrant Config (QCFG[7:0])

These pins define the S-RIO port width (x1, x2, x4) at RESET for all ports. QCFG[1:0] defines port width for Quadrant 0, QCFG[3:2] defines port width for Quadrant 1, QCFG[5:4] defines port width for Quadrant 2, and QCFG[7:6] defines port width for Quadrant 3. For more information, see Quadrant Configuration Pins QCFG[7:0].

### Frequency Select (FSEL[1:0])

FSEL1 pin defines the input reference clock, and FSEL0 pin defines the internal clock frequency, full or half rate.

### Multicast (MCAST)

The Multicast-Event Control Symbol Trigger (MCAST) pin provides an optional mechanism to trigger the generation of a Multicast-Event Control Symbol. The multicast-event control symbol allows a user-defined system event to be multicast throughout a system (for example, synchronously reset a system or its internal timers).

## 5. Configuration Pins

## Speed Select Pins SPD[2:0]

There are three port-speed selection pins that select the initial speed of the RapidIO ports (see Table 1). The RESET setting can be overridden by programming the PLL n Control 1 Register and Lane n Control Register (for more information, see "Lane and Port Speeds" in the *CPS-1432 User Manual*).

| Value on the Pins<br>(SPD2, SPD1, SPD0) | Port Rate (Gbaud) |

|-----------------------------------------|-------------------|

| 000                                     | 1.25              |

| 001                                     | 2.5               |

| 01X                                     | 5.0               |

| 100                                     | Reserved          |

| 101                                     | 3.125             |

| 11X                                     | 6.25              |

#### Table 1: Port Speed Selection Pin Values

### **Quadrant Configuration Pins QCFG[7:0]**

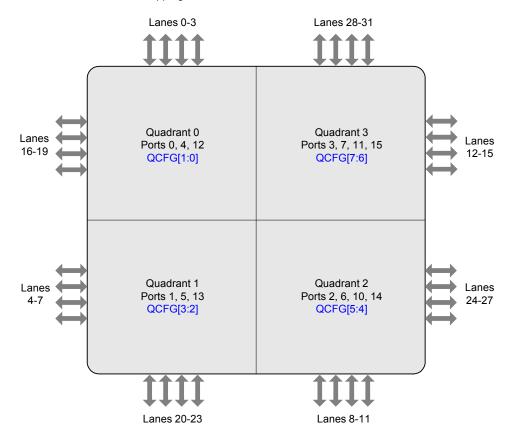

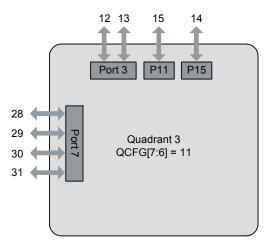

There are eight quadrant configuration selection pins, QCFG[7:0], or two pins per quadrant (see Figure 2). These pins configure the device's power-up settings for port width and lane to port mapping. After power-up these settings can be changed by updating the Quadrant Configuration Register (for more information, see "Lane to Port Mapping" in the *CPS-1432 User Manual*).

#### Figure 2: Quadrant Configuration using QCFG[7:0]

Figure 3 shows the relationship between the Quadrant, Port, and Lane settings, based on the configuration of the device's QCFG[7:6] pins.

Figure 3: Quadrant 3 Configuration Example - QCFG[7:6] = 11

The following describes the complete lane-to-port mapping options for the CPS-1432 based on the setting of the QCFG[7:0] pins.

|          |           | QCFG Pin |              |                                                            | Mapping |         |  |

|----------|-----------|----------|--------------|------------------------------------------------------------|---------|---------|--|

| Quadrant | QCFG Pins | Setting  | PLL          | Port Width                                                 | Port    | Lane(s) |  |

| 0        | QCFG[1:0] | 00       | 0            | 4x                                                         | 0       | 0–3     |  |

|          |           |          | 4            | 4x                                                         | 4       | 16–19   |  |

|          |           | 01       | 0            | 2x                                                         | 0       | 0–1     |  |

|          |           |          | 4            | 4x                                                         | 4       | 16–19   |  |

|          |           |          | 0 2x<br>Unde |                                                            | 12      | 2–3     |  |

|          |           | 10       |              |                                                            | efined  |         |  |

|          |           | 11       |              | Unde                                                       | efined  |         |  |

| 1        | QCFG[3:2] | 00       | 1            | 1         4x           5         4x           1         2x |         | 4–7     |  |

|          |           |          | 5            |                                                            |         | 20–23   |  |

|          |           | 01       | 1            |                                                            |         | 4–5     |  |

|          |           |          | 5            | 4x                                                         | 5       | 20–23   |  |

|          |           |          | 1            | 2x                                                         | 13      | 6–7     |  |

|          |           | 10       | Undefined    |                                                            |         |         |  |

|          |           | 11       |              | Unde                                                       | fined   |         |  |

#### Table 2: Lane to Port Mapping

|          |           | QCFG Pin |     |            | Ма   | pping   |

|----------|-----------|----------|-----|------------|------|---------|

| Quadrant | QCFG Pins | Setting  | PLL | Port Width | Port | Lane(s) |

| 2        | QCFG[5:4] | 00       | 2   | 4x         | 2    | 8–11    |

|          |           |          | 6   | 4x         | 6    | 24–27   |

|          |           | 01       | 2   | 2x         | 2    | 8–9     |

|          |           |          | 6   | 4x         | 6    | 24–27   |

|          |           |          | 2   | 2x         | 14   | 10–11   |

|          |           | 10       | 2   | 2x         | 2    | 8–9     |

|          |           |          | 6   | 2x         | 6    | 24–25   |

|          |           |          | 6   | 2x         | 10   | 26–27   |

|          |           |          | 2   | 2x         | 14   | 10–11   |

|          |           | 11       | 2   | 2x         | 2    | 8–9     |

|          |           |          | 6   | 4x         | 6    | 24–27   |

|          |           |          | 2   | 1x         | 10   | 11      |

|          |           |          | 2   | 1x         | 14   | 10      |

| 3        | QCFG[7:6] | 00       | 3   | 4x         | 3    | 12–15   |

|          |           |          | 7   | 4x         | 7    | 28–31   |

|          |           | 01       | 3   | 2x         | 3    | 12–13   |

|          |           |          | 7   | 4x         | 7    | 28–31   |

|          |           |          | 3   | 2x         | 15   | 14–15   |

|          |           | 10       | 3   | 2x         | 3    | 12–13   |

|          |           |          | 7   | 2x         | 7    | 28–29   |

|          |           |          | 7   | 2x         | 11   | 30–31   |

|          |           |          | 3   | 2x         | 15   | 14–15   |

|          |           | 11       | 3   | 2x         | 3    | 12–13   |

|          |           |          | 7   | 4x         | 7    | 28–31   |

|          |           |          | 3   | 1x         | 11   | 15      |

|          |           |          | 3   | 1x         | 15   | 14      |

Table 2: Lane to Port Mapping (Continued)

The CPS-1432 supports ports 0 to 15; however, ports 8 and 9 are not available to the device. In order to reduce power consumption, IDT recommends that these ports be disabled. Refer to the User Manual for the specific register.

## 6. Absolute Maximum Ratings

#### Table 3: Absolute Maximum Rating<sup>1</sup>

|                                                                                        |                                                                                     | Ra      | ting    |      |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|---------|---------|------|

| Symbol                                                                                 | Parameter                                                                           | Minimum | Maximum | Unit |

| V <sub>DD3</sub>                                                                       | V <sub>DD3</sub> voltage with respect to GND                                        | -0.5    | 3.6     | V    |

| V <sub>DD</sub>                                                                        | V <sub>DD</sub> voltage with respect to GND                                         | -0.5    | 1.2     | V    |

| V <sub>DDT</sub> V <sub>DDT</sub> voltage with respect to GNDS (V <sub>DDS</sub> = 0V) |                                                                                     | -0.5    | 1.2     | V    |

|                                                                                        | V <sub>DDT</sub> voltage with respect to GNDS (V <sub>DDS</sub> = 1.0V)             | -0.5    | 1.4     | V    |

| V <sub>DDA</sub> and V <sub>DDS</sub>                                                  | V <sub>DDS</sub> V <sub>DDA</sub> AND V <sub>DDS</sub> voltage with respect to GNDS |         | 1.2     | V    |

| T <sub>BIAS</sub> <sup>2</sup>                                                         | Temperature under bias                                                              | -55     | 125     | С    |

| T <sub>STG</sub>                                                                       | Storage temperature                                                                 | -65     | 150     | С    |

| T <sub>JN</sub> Junction temperature                                                   |                                                                                     | -       | 125     | С    |

| I <sub>OUT</sub> (for V <sub>DD3</sub> = 3.3V) DC output current                       |                                                                                     | -       | 30      | mA   |

| $I_{OUT}$ (for $V_{DD3}$ = 2.5V)                                                       | DC output current                                                                   | -       | 30      | mA   |

Notes:

- 1. Stresses greater than those listed under Absolute Maximum Ratings can cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods can affect reliability.

- 2. Ambient Temperature under DC Bias, no AC conditions. Can not exceed maximum Junction temperature.

- 3. IDT recommends not to exceed ripple voltage of 50 mV max on V<sub>DDT</sub>/V<sub>DDS</sub>/V<sub>DDA</sub> and 50 mV/100 mV (maximum) on V<sub>DD</sub>/V<sub>DD3</sub> respectively.

## 7. Recommended Operating Conditions

|                                                      |                                                                    | Rat     |                        |      |

|------------------------------------------------------|--------------------------------------------------------------------|---------|------------------------|------|

| Symbol <sup>2</sup>                                  | Parameter                                                          | Minimum | Maximum                | Unit |

| V <sub>DD3</sub> -supplied interfaces <sup>3 5</sup> | Input or I/O terminal voltage with respect to GND                  | -0.3    | V <sub>DD3</sub> + 0.3 | V    |

| V <sub>DD</sub>                                      | V <sub>DD</sub> voltage with respect to GND                        | 0.95    | 1.05                   | V    |

| $V_{DDA}$ and $V_{DDS}^4$                            | $V_{\text{DDA}}$ and $V_{\text{DDS}}$ voltage with respect to GNDS | 0.95    | 1.05                   | V    |

| V <sub>DDT</sub>                                     | V <sub>DDT</sub> voltage with respect to GNDS                      | 1.14    | 1.26                   | V    |

| V <sub>DD3</sub> and V <sub>DD3A</sub>               | V <sub>DD3</sub> voltage (3.3 V) with respect to GND               | 3.14    | 3.47                   | V    |

|                                                      | V <sub>DD3</sub> voltage (2.5 V) with respect to GND               | 2.4     | 2.6                    | V    |

#### Table 4: Recommended Operating Conditions<sup>1</sup>

Notes:

- The following power-up sequence is necessary in order for the device to function properly: The SerDes voltage (V<sub>DDS</sub>) needs to power-up first followed by SerDes voltage (V<sub>DDT</sub>). V<sub>DD</sub>, V<sub>DDA</sub>, and V<sub>DD3(a)</sub> can be powered up in any order. The device is not sensitive to supply rise and fall times, and thus these are not specified.

- 2. V<sub>DDT</sub>, V<sub>DDA</sub>, and V<sub>DDS</sub> share a common ground (GNDS). Core supply and ground are V<sub>DD</sub> and GND respectively.

- 3. V<sub>DD3</sub> can be operated at either 3.3V or 2.5V simply by providing that supply voltage. For those interfaces operating on this supply, this datasheet provides input and output specifications at each of these voltages.

- 4. V<sub>DDS</sub> and V<sub>DDA</sub> can be tied to a common power plane. V<sub>DD</sub> (core, digital supply) should have its own power plane. If the same voltage regulator is used for V<sub>DDS</sub>/V<sub>DDA</sub> and V<sub>DD</sub>, the V<sub>DDS</sub>/V<sub>DDA</sub> plane should be isolated to prevent noise from the V<sub>DD</sub> plane to couple onto the V<sub>DDS</sub>/V<sub>DDA</sub> plane.

- 5. This is a steady-state DC parameter that applies after the power supply has reached its nominal operating value. The voltage on any Input or I/O pin cannot exceed its corresponding supply voltage during power supply ramp up.

## 8. AC Test Conditions

| Input Pulse Levels               | GND to 3.0V / GND to 2.4V |

|----------------------------------|---------------------------|

| Input Rise / Fall Times          | 2 ns                      |

| Input Timing Reference<br>Levels | 1.5V / 1.25V              |

| Output Reference Levels          | 1.5V / 1.25V              |

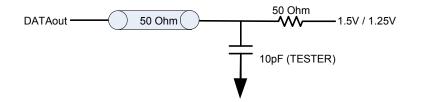

| Output Load                      | See Figure 4              |

#### Table 5: AC Test Conditions (V<sub>DD3</sub> = 3.3V / 2.5V): JTAG, I<sup>2</sup>C, RST

Figure 4: AC Output Test Load (JTAG)

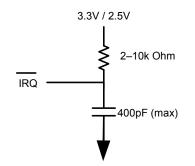

Note: The IRQ\_N pin is an open-drain driver. IDT recommends a weak pull-up resistor (2-10k Ohm) be placed on this pin to V<sub>DD3</sub>.

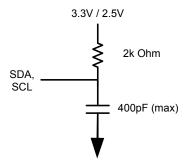

#### Figure 6: AC Output Test Load (I<sup>2</sup>C)

Note: The SDA and SCL pins are open-drain drivers. For information on the appropriate selection of pull-up resistors for each, see the *Philips PC Specification* [1].

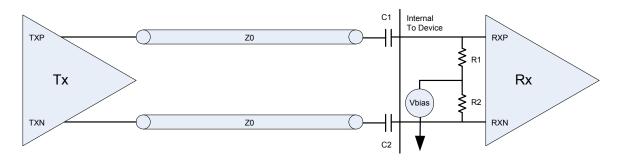

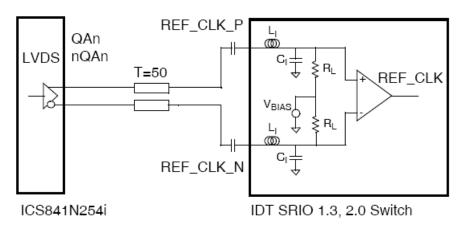

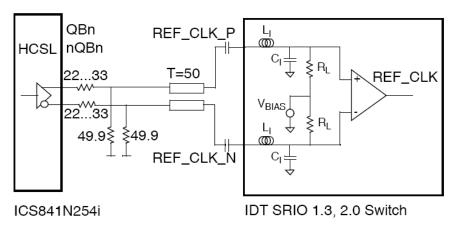

The characteristic impedance Z0 should be designed for 100 Ohms differential. An inline capacitor C1 and C2 at each input of the receiver provides AC-coupling and a DC-block. The IDT recommended values are 75 - 200nF for each. Thus, any DC bias differential between the two devices on the link is negated. The differential input resistance at the receiver is 100 Ohms, as defined in the *RapidIO Specification (Rev. 2.1)*. Thus, R1 and R2 are 50 Ohms each. Note that VBIAS is the internal bias voltage of the device's receiver.

## 9. Power Consumption

Heat generated by the packaged IC and increase in voltage supplies have an adverse effect on the device power consumption. In order to control its functional and maximum design temperature limits, IDT recommends at a minimum to use a heat sink. The typical and maximum power numbers provided below take into consideration the heat sink with the following characteristics, Theta  $Ja = 4.2^{\circ}C/W$  with 1m/s of airflow. For more information on thermal analysis, see Thermal Characteristics.

An estimate of the device power figure for an application usage can be determined by using the device's "Power Calculator" modeling tool available on the IDT secure site.

The *typical* power condition refers to nominal voltage for all rails and is 7.6W in total for all ports enabled as 3 4x, 9 2x and 2 1x at 6.25 Gbaud under 50% switch load.

The *maximum* power condition refers to maximum voltage for all rails and is 11.8W in total for all ports enabled as 3 4x, 9 2x and 2 1x at 6.25 Gbaud under 100% switch load.

|                    |                   |                                   | Power Supplies |             |                           |             |                              |             |                |             |                           |              |              |

|--------------------|-------------------|-----------------------------------|----------------|-------------|---------------------------|-------------|------------------------------|-------------|----------------|-------------|---------------------------|--------------|--------------|

|                    |                   | Core Supply<br>(V <sub>DD</sub> ) |                |             | Supply<br><sub>DS</sub> ) |             | Supply<br>V <sub>DDT</sub> ) |             | Supply<br>DDA) |             | upply<br><sub>DD3</sub> ) | То           | ıtal         |

| Line Rate<br>Gbaud | Current/<br>Power | Тур<br>1.0V                       | Max<br>1.05V   | Тур<br>1.0V | Max<br>1.05V              | Тур<br>1.2V | Max<br>1.26V                 | Тур<br>1.0V | Max<br>1.05V   | Тур<br>3.3V | Max<br>3.47V              | Typ<br>Power | Max<br>Power |

| 6.25               | Amps              | 4.46                              | 7.67           | 1.68        | 1.89                      | 0.96        | 1.04                         | 0.30        | 0.36           | 0.016       | 0.030                     |              |              |

|                    | Watts             | 4.46                              | 8.05           | 1.68        | 1.98                      | 1.15        | 1.31                         | 0.30        | 0.378          | 0.053       | 0.108                     | 7.64         | 11.83        |

| 5.0                | Amps              | 4.36                              | 7.58           | 1.56        | 1.74                      | 0.97        | 1.04                         | 0.27        | 0.33           | 0.016       | 0.030                     |              |              |

|                    | Watts             | 4.36                              | 7.96           | 1.56        | 1.83                      | 1.16        | 1.31                         | 0.27        | 0.347          | 0.053       | 0.108                     | 7.40         | 11.56        |

| 3.125              | Amps              | 4.20                              | 7.42           | 1.39        | 1.54                      | 0.96        | 1.04                         | 0.30        | 0.36           | 0.016       | 0.030                     |              |              |

|                    | Watts             | 4.20                              | 7.79           | 1.39        | 1.62                      | 1.15        | 1.31                         | 0.30        | 0.378          | 0.053       | 0.108                     | 7.09         | 11.21        |

| 2.5                | Amps              | 4.14                              | 7.37           | 1.33        | 1.46                      | 0.96        | 1.04                         | 0.27        | 0.33           | 0.016       | 0.030                     |              |              |

|                    | Watts             | 4.14                              | 7.74           | 1.33        | 1.53                      | 1.15        | 1.31                         | 0.27        | 0.347          | 0.053       | 0.108                     | 6.94         | 10.98        |

| 1.25               | Amps              | 4.04                              | 7.29           | 1.21        | 1.33                      | 0.96        | 1.04                         | 0.27        | 0.33           | 0.016       | 0.030                     |              |              |

|                    | Watts             | 4.04                              | 7.65           | 1.21        | 1.40                      | 1.15        | 1.31                         | 0.27        | 0.347          | 0.053       | 0.108                     | 6.72         | 10.82        |

#### Table 6: Power Consumption

Notes:

1. Typical conditions: V<sub>DD</sub>, V<sub>DDS</sub>, V<sub>DDA</sub> = 1.0V, V<sub>DDT</sub> = 1.2V, V<sub>DD3</sub> = 3.3V at Ambient Temperature of 60°C with heat sink (Theta Ja = 4.2°C/W @ 1m/s airflow).

2. Maximum conditions:  $V_{DD}$ ,  $V_{DDS}$ ,  $V_{DDA}$  = 1.05V,  $V_{DDT}$  = 1.26V,  $V_{DD3}$  = 3.47V at max Junction Temperature (125°C).

# 10. I<sup>2</sup>C Bus

The CPS-1432 is compliant with the  $l^2C$  specification [1]. This specification provides the functional information and electrical specifications associated with the  $l^2C$  bus, including signaling, addressing, arbitration, AC timing, and DC specifications. The CPS-1432 supports both master mode and slave mode, which is selected by MM\_N pin.

The I<sup>2</sup>C bus consists of the Serial Data (SDA) and Serial Clock (SCL) pins. It can be used to attach a CPU or a configuration memory. The I<sup>2</sup>C Interface supports Fast/Standard (F/S) mode (400/100 kHz).

## I<sup>2</sup>C Master Mode and Slave Mode

The CPS-1432 support both master mode and slave mode. The operating mode is selected by the MM\_N static configuration pin. For more information, see Signaling.

## I<sup>2</sup>C Device Address

The device address for the CPS-1432 is fully pin-defined by 10 external pins while in slave mode. This provides full flexibility in defining the slave address to avoid conflicting with other  $I^2C$  devices on a bus. The CPS-1432 can be operated as either a 10-bit addressable device or a 7-bit addressable device based on another external pin, address select (ADS). If the ADS pin is tied to  $V_{DD3}$ , then the CPS-1432 operates as a 10-bit addressable device address will be defined as ID[9:0]. If the ADS pin is tied to GND, then the CPS-1432 operates as a 7-bit addressable device with the device address defined by ID[6:0]. The addressing mode must be established at power-up and remain static throughout operation. Dynamic changes will result in unpredictable behavior.

| Pin | I <sup>2</sup> C Address Bit (pin_addr) |

|-----|-----------------------------------------|

| ID9 | 9 (don't care in 7-bit mode)            |

| ID8 | 8 (don't care in 7-bit mode)            |

| ID7 | 7 (don't care in 7-bit mode)            |

| ID6 | 6                                       |

| ID5 | 5                                       |

| ID4 | 4                                       |

| ID3 | 3                                       |

| ID2 | 2                                       |

| ID1 | 1                                       |

| ID0 | 0                                       |

#### Table 7: I<sup>2</sup>C Static Address Selection Pin Configuration

All of the CPS-1432's registers are addressable through I<sup>2</sup>C. These registers are accessed using 22-bit addresses and 32-bit word boundaries through standard reads and writes. These registers also can be accessed through the S-RIO and JTAG Interfaces.

## RENESAS

## Signaling

Communication with the CPS-1432 on the  $I^2C$  bus follows these three cases:

- 1. Suppose a master device wants to send information to the CPS-1432:

- Master device addresses CPS-1432 (slave)

- Master device (master-transmitter), sends data to CPS-1432 (slave- receiver)

- Master device terminates the transfer

- 2. If a master device wants to receive information from the CPS-1432:

- Master device addresses CPS-1432 (slave)

- Master device (master-receiver) receives data from CPS-1432 (slave- transmitter)

- Master device terminates the transfer

- 3. If CPS-1432 polls configuration image from external memory

- CPS-1432 addresses the memory

- Memory transmits the data

- CPS-1432 gets the data

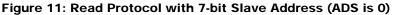

All signaling is fully compliant with I<sup>2</sup>C (for signaling information, see the Philips  $\ell^2C$  Specification) [1]. Standard signaling and timing waveforms are displayed below.

#### Connecting to Standard-, Fast-, and Hs-mode Devices

The CPS-1432 supports Fast/Standard (F/S) modes of operation. Per I<sup>2</sup>C specification, in mixed speed communication the CPS-1432 supports Hs- and Fast-mode devices at 400 Kbps, and Standard-mode devices at 100 Kbps. For information on speed negotiation on a mixed speed bus, see the I<sup>2</sup>C specification.

#### CPS-1432-Specific Memory Access (Slave Mode)

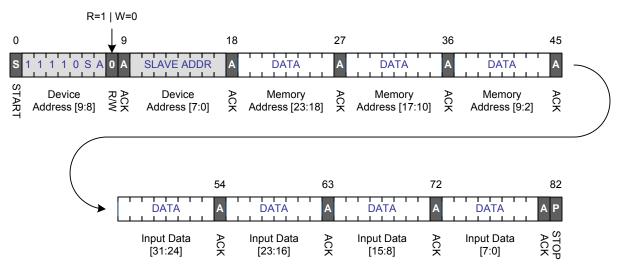

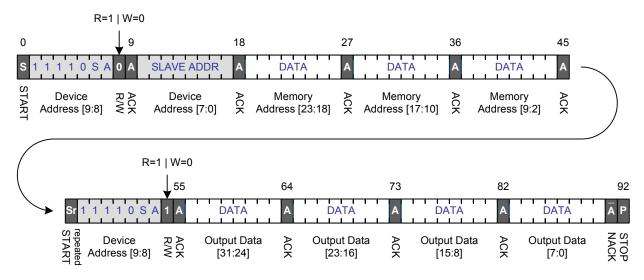

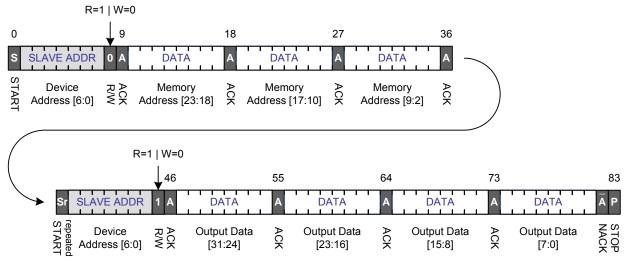

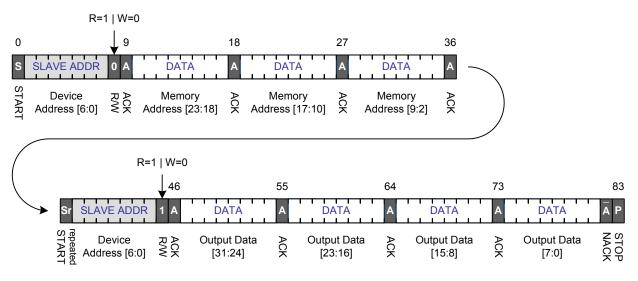

There is a CPS-1432-specific I<sup>2</sup>C memory access implementation. This implementation is fully I<sup>2</sup>C compliant. It requires the memory address to be specified during writes. This provides directed memory accesses through the I<sup>2</sup>C bus. Subsequent reads begin at the address specified during the last write.

The write procedure requires the 3 bytes (22 bits) of memory address to be provided following the device address. Thus, the following are required: device address – one or two bytes depending on 10-bit / 7-bit addressing, memory address – 3 bytes yielding 22 bits of memory address, and a 32-bit data payload – 4-byte words. To remain consistent with S-RIO standard maintenance packet memory address convention, the I<sup>2</sup>C memory address provided must be the 22 MSBs. Since I<sup>2</sup>C writes to memory apply to double-words (32 bits), the two LSBs are "don't care" as the LSBs correspond to word and byte pointers.

The read procedure has the memory address section of the transfer removed. Thus, to perform a read, the proper access would be to perform a write operation and issue a repeated start after the acknowledge bit following the third byte of memory address. Then, the master would issue a read command selecting the CPS-1432 through the standard device address procedure with the R/W bit high. Note that in 10-bit device address mode (ADS=1), only the two MSBs need be provided during this read. Data from the previously loaded address would immediately follow the device address protocol. A stop or repeated start can be issued anytime during the write data payload procedure, but must be before the final acknowledge; that is, canceling the write before the write operation is completed and performed. Also, the master would be allowed to access other devices attached to the I<sup>2</sup>C bus before returning to select the CPS-1432 for the subsequent read operation from the loaded address.

### **Read/Write Figures**

Figure 8: Write Protocol with 10-bit Slave Address (ADS is 1)

I<sup>2</sup>C writes to memory align on 32-bit word boundaries, thus the 24 address MSBs must be provided while the two LSBs associated with word and byte pointers are "don't care", and therefore are not transmitted.

Figure 9: Read Protocol with 10-bit Slave Address (ADS is 1)

Figure 10: Write Protocol with 7-bit Slave Address (ADS is 0)

I<sup>2</sup>C writes to memory align on 32-bit word boundaries, thus the 24 address MSBs must be provided while the two LSBs associated with word and byte pointers are "don't care", and therefore are not transmitted.

#### CPS-1432 Configuration and Image (Master mode)

There is both a power-up master and a command master mode. If powered up in master mode, the CPS-1432 polls configuration image from external memory after the device reset sequence has completed. Once the device has completed its configuration sequence, it will revert to slave mode. Through a configuration register write, the device can be commanded to enter master mode, which provides more configuration sequence flexibility. For more information, see the "I<sup>2</sup>C Interface" chapter in the *CPS-1432 User Manual*.

## I<sup>2</sup>C DC Electrical Specifications

Note that the ADS and ID pins will all run off the  $V_{DD3}$  (3.3V/2.5V) power supply, and these pins are required to be fixed during operation. Thus, these pins must be statically tied to the 3.3V/2.5V supply or GND.

Table 8 to Table 10 list the SDA and SCL electrical specifications for F/S-mode  $I^2C$  devices.

At recommended operating conditions with V<sub>DD3</sub> =  $3.3V \pm 5\%$ .

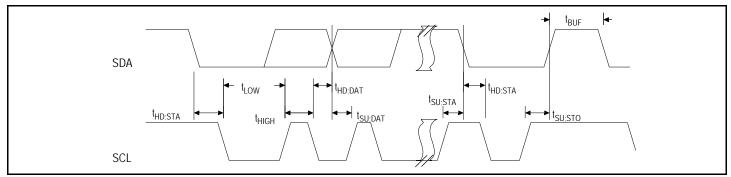

| Parameter                                                                                       | Symbol           | Min                       | Мах                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|---------------------------|-----------------------------|------|

| Input high voltage level                                                                        | V <sub>IH</sub>  | 0.7 x V <sub>DD3</sub>    | V <sub>DD3(max)</sub> + 0.5 | V    |

| Input low voltage level                                                                         | V <sub>IL</sub>  | -0.5                      | 0.3 x V <sub>DD3</sub>      | V    |

| Hysteresis of Schmitt trigger inputs                                                            | V <sub>HYS</sub> | 0.05 x V <sub>DD3</sub>   | -                           | V    |

| Output low voltage                                                                              | V <sub>OL</sub>  | 0                         | 0.4                         | ns   |

| Output fall time from $V_{IH(min)}$ to $V_{IL(max)}$ with a bus capacitance from 10pF to 400pF  | t <sub>OF</sub>  | 20 + 0.1 x C <sub>b</sub> | 250                         | ns   |

| Pulse width of spikes which must be suppressed by the input filter                              | t <sub>SP</sub>  | 0                         | 50                          | ns   |

| Input current each I/O pin (input voltage is between 0.1 x $V_{DD3}$ and 0.9 x $V_{DD3}$ (max)) | I                | -10                       | 10                          | uA   |

| Capacitance for each I/O pin                                                                    | Cl               | -                         | 10                          | pF   |

#### Table 8: I<sup>2</sup>C DC Electrical Specifications (3.3V)

At recommended operating conditions with  $V_{DD3} = 2.5V \pm 100 \text{mV}$ .

| Table 9: I <sup>2</sup> C DC Electrical Specifications (2.5 | σV) |

|-------------------------------------------------------------|-----|

|-------------------------------------------------------------|-----|

| Parameter                                                                                       | Symbol           | Min                       | Мах                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|---------------------------|-----------------------------|------|

| Input high voltage level                                                                        | V <sub>IH</sub>  | 0.7 x V <sub>DD3</sub>    | V <sub>DD3(max)</sub> + 0.1 | V    |

| Input low voltage level                                                                         | V <sub>IL</sub>  | -0.5                      | 0.3 x V <sub>DD3</sub>      | V    |

| Hysteresis of Schmitt trigger inputs                                                            | V <sub>HYS</sub> | 0.05 x V <sub>DD3</sub>   | -                           | V    |

| Output low voltage                                                                              | V <sub>OL</sub>  | 0                         | 0.4                         | ns   |

| Output fall time from $V_{IH(min)}$ to $V_{IL(max)}$ with a bus capacitance from 10pF to 400pF  | t <sub>OF</sub>  | 20 + 0.1 x C <sub>b</sub> | 250                         | ns   |

| Pulse width of spikes which must be<br>suppressed by the input filter                           | t <sub>SP</sub>  | 0                         | 50                          | ns   |

| Input current each I/O pin (input voltage is between 0.1 x $V_{DD3}$ and 0.9 x $V_{DD3}$ (max)) | I                | -10                       | 10                          | uA   |

| Capacitance for each I/O pin                                                                    | CI               | -                         | 10                          | pF   |

## I<sup>2</sup>C AC Electrical Specifications

Table 10: Specifications of the SDA and SCL Bus Lines for F/S-mode I<sup>2</sup>C Bus Devices

| Signal                                           | Symbol  | Reference<br>Edge | Standard<br>Mode |      | Fast<br>Mode |     | Unit |

|--------------------------------------------------|---------|-------------------|------------------|------|--------------|-----|------|

| l <sup>2</sup> C <sup>(1,4)</sup>                |         |                   | Min              | Мах  | Min          | Мах |      |

| SCL                                              | fscl    | none              | 0                | 100  | 0            | 400 | kHz  |

|                                                  | thd;sta |                   | 4.0              | -    | 0.6          | -   | us   |

|                                                  | tr      |                   | -                | 1000 | -            | 300 | ns   |

|                                                  | tF      |                   | -                | 300  | -            | 300 | ns   |

| SDA <sup>(2,3)</sup>                             | tsu;dat | SCL rising        | 250              | -    | 100          | -   | ns   |

|                                                  | thd;dat | SCL falling       | 0                | 3.45 | 0            | 0.9 | us   |

|                                                  | tr      | -                 | -                | 1000 | 10           | 300 | ns   |

|                                                  | tF      | -                 | -                | 300  | 10           | 300 | ns   |

| Start or repeated start                          | tsu;sta | SDA falling       | 4.7              | -    | 0.6          | -   | us   |

| condition                                        | tsu;sto |                   | 4.0              | -    | 0.6          | -   | us   |

| Stop condition                                   | tsu;sto | SDA rising        | 4.0              | -    | 0.6          | -   | us   |

| Bus free time between a stop and start condition | tBUF    | -                 | 4.7              | -    | 1.3          | -   | us   |

| Capacitive load for each bus line                | Св      | -                 | -                | 400  | -            | 400 | pF   |

Notes:

1. For more information, see the  $\ell$ *C-Bus Specification* by Philips Semiconductor.

- 2. A device must internally provide a hold time of at least 300 ns for the SDA signal (referred to the VIHMIN of the SCL signal) to bridge the undefined region of the falling edge of SCL.

- 3. The maximum thd;DAT has only to be met if the device does not stretch the LOW period (tLow) of the SCL signal.

- 4. A Fast-mode I<sup>2</sup>C-bus device can be used in a Standard-mode I<sup>2</sup>C-bus system, but the requirement  $t_{SU;DAT} \ge 250$  ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{RMAX} + t_{SU;DAT} = 1000 + 250 = 1250$  ns (according to the Standard-mode *I*<sup>2</sup>C-*Bus Specification*) before the SCL line is released.

## RENESAS

## I<sup>2</sup>C Timing Waveforms

Figure 12: I<sup>2</sup>C Timing Waveforms

# 11. Interrupt (IRQ\_N) Electrical Specifications

At recommended operating conditions with  $V_{DD3}$  = 3.3V  $\pm$  5%.

#### Table 11: IRQ\_N Electrical Specifications (V<sub>DD3</sub> = 3.3V ± 5%)

| Parameter                                                                                       | Symbol          | Min | Мах | Unit |

|-------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| Output low voltage (I <sub>OL</sub> = 4mA, V <sub>DD3</sub> = Min.)                             | V <sub>OL</sub> | 0   | 0.4 | V    |

| Output fall time from $V_{IH(min)}$ to $V_{IL(max)}$ with a bus capacitance from 10pF to 400pF  | t <sub>OF</sub> | -   | 25  | ns   |

| Input current each I/O pin (input voltage is between 0.1 x $V_{DD3}$ and 0.9 x $V_{DD3}$ (max)) | Ι <sub>Ι</sub>  | -10 | 10  | uA   |

| Capacitance for IRQ_N                                                                           | Cl              | -   | 10  | pF   |

At recommended operating conditions with V<sub>DD3</sub> =  $2.5V \pm 100mV$ .

| ······                                                                                          |                 |     |     |      |  |  |

|-------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|--|--|

| Parameter                                                                                       | Symbol          | Min | Мах | Unit |  |  |

| Output low voltage (I <sub>OL</sub> = 2mA, V <sub>DD3</sub> = Min.)                             | V <sub>OL</sub> | 0   | 0.4 | V    |  |  |

| Output fall time from $V_{IH(min)}$ to $V_{IL(max)}$ with a bus capacitance from 10pF to 400pF  | t <sub>OF</sub> | -   | 25  | ns   |  |  |

| Input current each I/O pin (input voltage is between 0.1 x $V_{DD3}$ and 0.9 x $V_{DD3}$ (max)) | Ι <sub>Ι</sub>  | -10 | 10  | uA   |  |  |

| Capacitance for IRQ_N                                                                           | Cl              | -   | 10  | pF   |  |  |

#### Table 12: IRQ\_N Electrical Specifications (V<sub>DD3</sub> = 2.5V ± 100mV)

#### Figure 13: IRQ\_N Timing Diagram

The IRQ\_N pin is an open-drain driver. IDT recommends a weak pull-up resistor (2-10k Ohm) be placed on this pin to V<sub>DD3</sub>. The IRQ\_N pin goes active low when any special error filter error flag is set, and is cleared when all error flags are reset.

# 12. Configuration (Static) Pin Specification

The following are the configuration pins this specification applies to; FSEL[1:0], MCAST<sup>2</sup>, RST\_N, QCFG[7:0] and SPD[2:0].

|                    |                 | Min  |      | M    |      |      |

|--------------------|-----------------|------|------|------|------|------|

| Parameter          | Symbol          | 2.5V | 3.3V | 2.5V | 3.3V | Unit |

| Input Low Voltage  | V <sub>IL</sub> | -0.3 | -0.3 | 0.7  | 0.8  | V    |

| Input High Voltage | V <sub>IH</sub> | 1.7  | 2.0  | 2.8  | 3.6  | V    |

#### Table 13: Configuration Pin Electrical Specification<sup>1</sup>

Notes:

- 1. Configuration pins must be set prior to or coincident with reset de-assertion and remain static following reset de-assertion. Any change on the configuration pins after reset is de-asserted can result in unexpected behavior.

- 2. The MCAST pin is asynchronous signal and sampled on the rising edge of the internal core clock.

The following internal pull-up resistor specification applies to following configuration pins; FSEL[1:0], MM\_N, QCFG[7:0], TDI, TMS and TRST\_N.

#### Table 14: Pull-up Resistor Specification

| Parameter               | Min | Тур | Мах | Unit   |

|-------------------------|-----|-----|-----|--------|

| Pull-up Resistor Values | 29  | 39  | 63  | K Ohms |

# 13. S-RIO Ports

### Overview

The CPS-1432's SerDes are in full compliance to the RapidIO AC specifications for the LP-Serial Physical Layer [5]. This section provides those specifications for reference only; the user should see the specification for complete requirements.

Chapter 9 of the LP-Serial Physical Layer Specification, "1.25 Gbaud, 2.5 Gbaud, and 3.125 Gbaud LP-Serial Links" defines Level I links compatible with the 1.3 version of the Physical Layer Specification, that supports throughput rates of 1.25, 2.5, and 3.125 Gbaud. Chapter 10 of the specification, "5 Gbaud and 6.25 Gbaud LP-Serial Links" defines Level II links that support throughput rates of 5 and 6.25 Gbaud.

A Level I link should:

- Allow 1.25, 2.5, or 3.125 Gbaud rates

- Support AC coupling

- Support hot swap

- · Support short run (SR) and long run (LR) links achieved with two transmitters

- · Support single receiver specification that will accept signals from both the short run and long run transmitter specifications

- Achieve Bit Error Ratio of lower than 10<sup>-12</sup> per lane

A Level II link should:

- Allow 5 or 6.25 Gbaud baud rates

- Support AC coupling

- Support hot swap

- · Support short run (SR), medium run (MR), and long run (LR) links achieved with two transmitters and two receivers

- Achieve Bit Error Ratio of lower than 10<sup>-15</sup> per lane

Together, these specifications allow for solutions ranging from simple chip-to-chip interconnect to board-to-board interconnect driving two connectors across a backplane. The faster and wider electrical interfaces specified here are required to provide higher density and/or lower cost interfaces.

The short run defines a transmitter and a receiver that should be used mainly for chip-to-chip connections on either the same printed circuit board or across a single connector. This covers the case where connections are made to a mezzanine (daughter) card. The smaller swings of the short run specification reduces the overall power used by the transceivers.

The long run defines a transmitter and receiver that use larger voltage swings and channel equalization that allows a user to drive signals across two connectors and backplanes.

The two transmitter specifications allows for a medium run specification that also uses larger voltage swings that can drive signals across a backplane but simplifies the receiver requirements to minimize power and complexity. This option has been included to allow the system integrator to deploy links that take advantage of either channel materials and/or construction techniques that reduce channel loss to achieve lower power systems.

The electrical specifications are based on loss, jitter, and channel cross-talk budgets and defines the characteristics required to communicate between a transmitter and a receiver using nominally 100 Ohm differential copper signal traces on a printed circuit board. Rather than specifying materials, channel components, or configurations, this specification focuses on effective channel characteristics. Therefore, a short length of poorer material should be equivalent to a longer length of premium material. A 'length' is effectively defined in terms of its attenuation rather than physical distance.

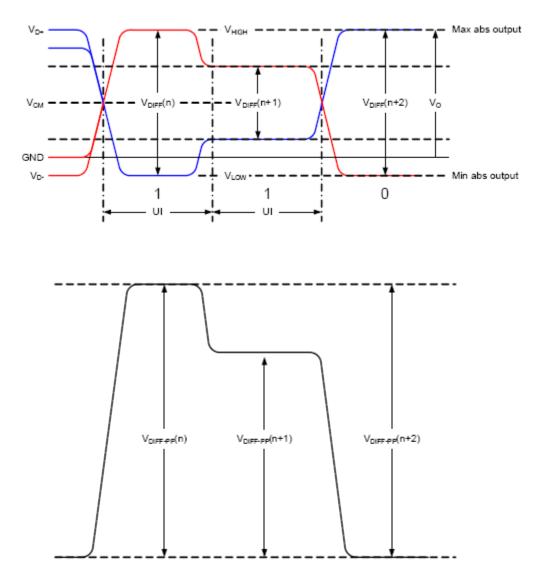

### **Definition of Amplitude and Swing**

LP-Serial links use differential signaling. This section defines the terms used in the description and specification of these differential signals. Figure 14 shows how these signals are defined and sets out the relationship between absolute and differential voltage amplitude. The figure shows waveforms for either the transmitter output (TD and TD\_N) or a receiver input (RD and RD\_N).

Each signal swings between the voltages VHIGH and VLOW where

VHIGH > VLOW

The differential voltage,  $V_{\text{DIFF}}$  is defined as

$V_{DIFF} = V_{D+} - V_{D-}$

where  $V_{D+}$  is the voltage on the positive conductor and  $V_{D-}$  is the voltage on the negative conductor of a differential transmission line.  $V_{DIFF}$  represents either the differential output signal of the transmitter,  $V_{OD}$ , or the differential input signal of the receiver,  $V_{ID}$  where

$V_{OD} = V_{TD} - V_{\overline{TD}}$

and

$V_{ID} = V_{RD} - V_{\overline{RD}}$

## RENESAS

The common mode voltage, V<sub>CM</sub>, is defined as the average or mean voltage present on the same differential pair. Therefore

$V_{CM} = |V_{D+} + V_{D-}| / 2$

The maximum value, or the peak-to-peak differential voltage, is calculated on a per unit interval and is defined as

$V_{DIFFp-p} = 2 x max | V_{D+} - V_{D-} |$

because the differential signal ranges from V\_D+ - V\_D- to -(V\_D+ - V\_D-)

To illustrate these definitions using real values, consider the case of a CML (Current Mode Logic) transmitter and each of its outputs, TD and TD\_N, has a swing that goes between  $V_{HIGH} = 2.5V$  and  $V_{LOW} = 2.0V$ , inclusive. Using these values the common mode voltage is calculated to be 2.25 V and the single-ended peak voltage swing of the signals TD and TD\_N is 500 mVpp. The differential output signal ranges between 500 mV and -500 mV, inclusive. therefore the peak-to-peak differential voltage is 1000 mVppd.

## 1.25, 2.5, and 3.125 Gbaud LP-Serial Links

This section explains the requirements for Level I RapidIO LP-Serial short and long run electrical interfaces of nominal baud rates of 1.25, 2.5, and 3.125 Gbaud using NRZ coding (thus, 1 bit per symbol at the electrical level). The CPS-1432's SerDes meet all of the requirements listed below. The electrical interface is based on a high speed, low voltage logic with a nominal differential impedance of 100 Ohm. Connections are point-to-point balanced differential pair and signaling is unidirectional.

The level of links defined in this section are identical to those defined in the *RapidIO Specification (Rev. 1.3)*, 1x/4x LP-Serial Electrical Specification.

### Equalization

With the use of high speed serial links, the interconnect media will cause degradation of the signal at the receiver. Effects such as Inter-Symbol Interference (ISI) or data dependent jitter are produced. This loss can be large enough to degrade the eye opening at the receiver beyond what is allowed in the specification. To negate a portion of these effects, equalization can be used in the transmitter and/or receiver, but it is not required at baud rates less than 3.5 Gbaud.

#### Explanatory Note on Level I Transmitter and Receiver Specifications

AC electrical specifications are provided for the transmitter and receiver. Long run and short run interfaces at three baud rates are described.

The parameters for the AC electrical specifications are guided by the XAUI electrical interface specified in Clause 47 of IEEE 802.3ae-2002.[1] The goal of this standard is that electrical designs for Level I electrical designs can reuse XAUI, suitably modified for applications at the baud intervals and runs described herein.

## Level I Electrical Specification

#### Level I Transmitter Characteristics

Level I LP-Serial transmitter electrical and timing specifications are stated in the text and tables of this section. The differential return loss, S11, of the transmitter in each case must be better than:

-10 dB for (Baud Frequency) / 10 < Freq(f) < 625 MHz, and

-10 dB + 10log(f/625 MHz) dB for 625 MHz <= Freq(f) <= Baud Frequency

The reference impedance for the differential return loss measurements is 100 Ohm resistive. Differential return loss includes contributions from on-chip circuitry, chip packaging and any off-chip components related to the driver. The output impedance requirement applies to all valid output levels.

The CPS-1432 satisfies the specification requirement that the 20%-80% rise/fall time of the transmitter, as measured at the transmitter output, in each case has a minimum value 60 ps.

Similarly, the timing skew at the output of an LP-Serial transmitter between the two signals that comprise a differential pair does not exceed 25 ps at 1.25 Gbaud, 20 ps at 2.5 Gbaud, and 15 ps at 3.125 Gbaud.

#### Level I Short Run Transmitter Specifications

| Symbol          | Characteristics                                                         | Reference                | Min   | Тур | Мах        | Units |

|-----------------|-------------------------------------------------------------------------|--------------------------|-------|-----|------------|-------|

| T_Baud          | Baud Rate                                                               | Section 9.4.1.2          | 1.25  | -   | 3.125      | Gbaud |

| V <sub>O</sub>  | Absolute Output Voltage                                                 | Section 9.4.1.3          | -0.40 | -   | 2.30       | Volts |

| T_Vdiff         | Output Differential Voltage<br>(into floating load Rload = 100 Ohm)     | Section 9.4.1.3          | 500   | -   | 1000       | mVppd |

| T_Rd            | Differential Resistance                                                 | Section 9.4.1.5          | 80    | 100 | 120        | ohm   |

| T_tr, T_tf      | Recommended output rise and fall times (20% to 80%)                     | Section 9.4.1.4          | 60    | -   | -          | ps    |

| T_SDD22         | Differential Output Return Loss<br>(T_baud/10 < f < T_baud/2)           | Section 9.4.1.6          | -     | -   | -          | dB    |

|                 | Differential Output Return Loss<br>(T_baud/10 <u>&lt;</u> f < T_baud/2) |                          | -     | -   | -          | dB    |

| T_TCC22         | Common Mode Return Loss<br>(625 MHz <u>&lt;</u> f <u>&lt;</u> T_baud)   | Section 9.4.1.6          | -     | -   | Note 3     | dB    |

| T_Ncm           | Transmitter Common Mode Noise <sup>1</sup>                              |                          | -     | -   | Note 4     | mVppd |

| T_Vcm           | Output Common Mode Voltage                                              | Load Type 0 <sup>2</sup> | 0     | -   | 2.1        | V     |

| S <sub>MO</sub> | Multiple output skew, $N \le 4$                                         | Section 9.4.1.7          | -     | -   | 1000       | ps    |

| S <sub>MO</sub> | Multiple output skew, N > 4                                             | Section 9.4.1.7          | -     | -   | 2UI + 1000 | ps    |

| UI              | Unit Interval                                                           | -                        | 320   | -   | 800        | ps    |

Notes:

- 1. For all Load Types: R\_Rdin = 100 Ohm +/- 20 Ohm.

- 2. Load Type 0 with min. T\_Vdiff, AC-coupling or floating load.

- 3. It is suggested that T\_SCC22 be -6 dB to be compatible with Level II transmitter requirements.

- 4. It is suggested that T\_Ncm be limited to 5% of T\_Vdiff to be compatible with Level II transmitter requirements.

#### Level I Long Run Transmitter Specifications

#### Table 16: Level I Long Run Transmitter AC Timing Specifications

| Characteristics                                                       | Symbol          | Reference                | Min   | Тур | Мах        | Units |

|-----------------------------------------------------------------------|-----------------|--------------------------|-------|-----|------------|-------|

| Baud Rate                                                             | T_Baud          | Section 9.4.2.2          | 1.25  | -   | 3.125      | Gbaud |

| Absolute Output Voltage                                               | V <sub>O</sub>  | Section 9.4.2.3          | -0.40 | -   | 2.30       | Volts |

| Output Differential Voltage<br>(into floating load Rload = 100 Ohm)   | T_Vdiff         | Section 9.4.2.3          | 800   | -   | 1600       | mVppd |

| Differential Resistance                                               | T_Rd            | Section 9.4.1.5          | 80    | 100 | 120        | ohm   |

| Recommended output rise and fall<br>times<br>(20% to 80%)             | T_tr, T_tf      | -                        | 60    | -   | -          | ps    |

| Differential Output Return Loss<br>(T_baud/10 < f < T_baud/2)         | T_SDD22         | Section 9.4.1.6          | -     | -   | -          | dB    |

| Differential Output Return Loss<br>(T_baud/10 < f < T_baud/2)         |                 |                          | -     | -   | -          | dB    |

| Common Mode Return Loss<br>(625 MHz <u>&lt;</u> f <u>&lt;</u> T_baud) | T_TCC22         | Section 9.4.1.6          | -     | -   | Note 3     | dB    |

| Transmitter Common Mode Noise <sup>1</sup>                            | T_Ncm           |                          | -     | -   | Note 4     | mVppd |

| Output Common Mode Voltage                                            | T_Vcm           | Load Type 0 <sup>2</sup> | 0     | -   | 2.1        | V     |

| Multiple output skew, N $\leq$ 4                                      | S <sub>MO</sub> | -                        | -     | -   | 1000       | ps    |

| Multiple output skew, N > 4                                           | S <sub>MO</sub> | -                        | -     | -   | 2UI + 1000 | ps    |

| Unit Interval                                                         | UI              | -                        | 320   | -   | 800        | ps    |

Notes:

1. For all Load Types: R\_Rdin = 100 Ohm +/- 20 Ohm.

2. Load Type 0 with min. T\_Vdiff, AC-coupling or floating load.

3. It is suggested that T\_SCC22 be -6 dB to be compatible with Level II transmitter requirements.

4. It is suggested that T\_Ncm be limited to 5% of T\_Vdiff to be compatible with Level II transmitter requirements.

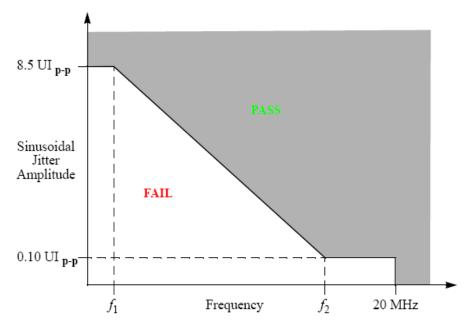

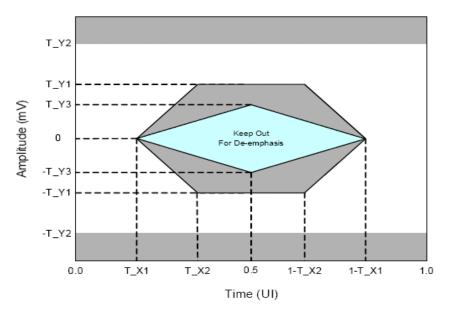

For each baud rate at which the LP-Serial transmitter is specified to operate, the output eye pattern of the transmitter falls entirely within the unshaded portion of the Transmitter Output Compliance Mask displayed in Figure 15 when measured at the output pins of the device and the device is driving a 100 Ohm  $\pm$  5% differential resistive load. The specification allows the output eye pattern of a LP-Serial transmitter that implements pre-emphasis (to equalize the link and reduce inter-symbol interference) to only comply with the Transmitter Output Compliance Mask when pre-emphasis is disabled or minimized

Figure 15: Transition Symbol Transmit Eye Mask

| Characteristics                                 | Symbol  | Near-End<br>Short Run<br>Value | Near-End<br>Long Run<br>Value | Units |

|-------------------------------------------------|---------|--------------------------------|-------------------------------|-------|

| Eye Mask                                        | T_X1    | 0.17                           | 0.17                          | UI    |

| Eye Mask                                        | T_X2    | 0.39                           | 0.39                          | UI    |

| Eye Mask                                        | T_Y1    | 250                            | 400                           | mV    |

| Eye Mask                                        | T_Y2    | 500                            | 800                           | mV    |

| Eye Mask                                        | T_Y3    | N/A                            | N/A                           | mV    |

| Uncorrelated Bounded High<br>Probability Jitter | T_UBHPJ | 0.17                           | 0.17                          | Ulpp  |

| Duty Cycle Distortion                           | T_DCD   | 0.05                           | 0.05                          | Ulpp  |

| Total Jitter                                    | T_TJ    | 0.35                           | 0.35                          | Ulpp  |

Table 17: Level I Near-End (Tx) Template Intervals