# IDT<sub>®</sub> Tsi577 Serial RapidIO Switch

**User Manual**

June 6, 2016

#### GENERAL DISCLAIMER

Integrated Device Technology, Inc. (1DT') reserves the right to make changes to its products or specifications at any time, without notice, in order to improve design or performance. IDT does not assume responsibility for use of any circuitry described herein other than the circuitry embodied in an IDT product. Disclosure of the information herein does not convey a license or any other right, by implication or otherwise, in any patent, trademark, or other intellectual property right of IDT. IDT products may contain errata which can affect product performance to a minor or immaterial degree. Current characterized errata will be made available upon request. Items identified herein as "reserved" or "undefined" are reserved for future definition. IDT does not assume responsibility for conflicts or incompatibilities arising from the future definition of such items. IDT products have not been designed, tested, or manufactured for use in, and thus are not warranted for, applications where the failure, malfunction, or any inaccuracy in the application carries a risk of death, serious bodily injury, or damage to tangible property. Code examples provided herein by IDT are for illustrative purposes only and should not be relied upon for developing applications. Any use of such code examples shall be at the user's sole risk.

Copyright  $^{\odot}$  2016 Integrated Device Technology, Inc. All Rights Reserved.

$The \ IDT \ logo \ is \ registered \ to \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ are \ Technology, \ Inc. \ IDT \ and \ CPS \ are \ trademarks \ of \ Integrated \ Device \ Technology, \ Inc. \ IDT \ are \ Technology, \ Inc. \ IDT \ are \ Technology, \ IDT \ are \ Technolo$

| Abo | out th                   | nis Do     | cument                       | 19 |  |  |  |  |

|-----|--------------------------|------------|------------------------------|----|--|--|--|--|

|     | Scope                    | e          |                              | 19 |  |  |  |  |

|     | Docu                     | ment Co    | nventions                    | 19 |  |  |  |  |

|     | Revis                    | sion Histo | ory                          | 20 |  |  |  |  |

| 1.  | Eur                      | etions     | al Overview                  | 22 |  |  |  |  |

| 1.  |                          |            |                              |    |  |  |  |  |

|     | 1.1                      |            | Overview                     |    |  |  |  |  |

|     |                          | 1.1.1      | Typical Applications         |    |  |  |  |  |

|     | 1.0                      | 1.1.2      | Features                     |    |  |  |  |  |

|     | 1.2                      |            | RapidIO Interface            |    |  |  |  |  |

|     |                          | 1.2.1      | Features                     |    |  |  |  |  |

|     |                          | 1.2.2      | Transaction Flow Overview    |    |  |  |  |  |

|     |                          | 1.2.3      | Maintenance Requests         |    |  |  |  |  |

|     |                          | 1.2.4      | Control Symbols.             |    |  |  |  |  |

|     | 1.3                      |            | ast Engine                   |    |  |  |  |  |

|     |                          | 1.3.1      | Multicast Operation          |    |  |  |  |  |

|     |                          | 1.3.2      | Features                     |    |  |  |  |  |

|     | 1.4                      |            | RapidIO Electrical Interface |    |  |  |  |  |

|     | 1.5                      |            | al Switching Fabric (ISF)    |    |  |  |  |  |

|     | 1.6                      |            |                              |    |  |  |  |  |

|     | 1.7                      |            |                              |    |  |  |  |  |

|     | 1.8                      |            | Interface                    |    |  |  |  |  |

|     | 1.9                      | Port Ni    | umbering                     | 37 |  |  |  |  |

| 2.  | Serial RapidIO Interface |            |                              |    |  |  |  |  |

|     | 2.1                      | Overvi     | ew                           | 39 |  |  |  |  |

|     |                          | 2.1.1      | Features                     | 39 |  |  |  |  |

|     |                          | 2.1.2      | Transaction Flow Overview    | 40 |  |  |  |  |

|     |                          | 2.1.3      | Maintenance Requests         | 40 |  |  |  |  |

|     |                          | 2.1.4      | Control Symbols.             | 40 |  |  |  |  |

|     | 2.2                      | Transa     | ction Flow                   | 41 |  |  |  |  |

|     | 2.3                      | Lookuj     | p Tables                     | 41 |  |  |  |  |

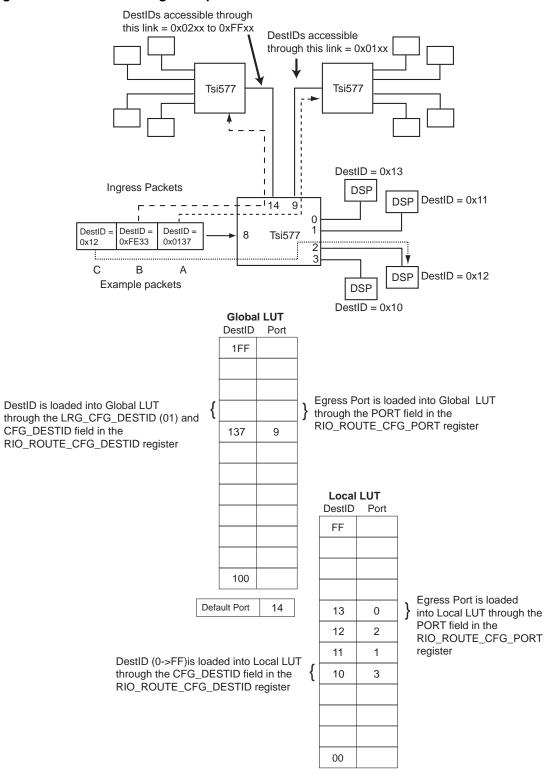

|     |                          | 2.3.1      | Filling the Lookup Tables    | 42 |  |  |  |  |

|     |                          | 2.3.2      | LUT Modes                    | 44 |  |  |  |  |

|     |                          | 2.3.3      | Flat Mode                    | 44 |  |  |  |  |

|     |                          | 2.3.4      | Hierarchical Mode            | 49 |  |  |  |  |

|     |                          | 2.3.5      | Mixed Mode of Operation      | 53 |  |  |  |  |

|     |                          | 2.3.6      | Lookup Table Parity          | 53 |  |  |  |  |

|     |                          | 2.3.7      | Lookup Table Error Summary   | 53 |  |  |  |  |

|     |                          | 2.3.8      | Lookup Table Entry States    | 54 |  |  |  |  |

|     | 2.4                      | Mainte     | enance Packets               | 56 |  |  |  |  |

|    | 2.5  | Multicast-Event Control Symbols                            | 58 |

|----|------|------------------------------------------------------------|----|

|    |      | 2.5.1 MCS Reception                                        | 58 |

|    |      | 2.5.2 Generating an MCS                                    | 59 |

|    |      | 2.5.3 Restrictions                                         | 59 |

|    | 2.6  | Reset Control Symbol Processing                            | 60 |

|    | 2.7  | Data Integrity Checking                                    | 60 |

|    |      | 2.7.1 Packet Data Integrity Checking                       | 60 |

|    |      | 2.7.2 Control Symbol Data Integrity Checking               | 60 |

|    | 2.8  | Time-to-Live (TTL) Counter                                 | 60 |

|    |      | 2.8.1 Operation                                            | 61 |

|    | 2.9  | Error Management                                           | 63 |

|    |      | 2.9.1 Software Assisted Error Recovery                     | 63 |

|    | 2.10 | Hot Insertion and Hot Extraction.                          | 64 |

|    |      | 2.10.1 Hot Insertion                                       | 65 |

|    |      | 2.10.2 Hot Extraction                                      | 66 |

|    |      | 2.10.3 Hot Extraction System Notification.                 | 67 |

|    | 2.11 | Loss of Lane Synchronization                               |    |

|    |      | 2.11.1 Dead Link Timer                                     | 69 |

|    |      | 2.11.2 Lane Sync Timer                                     | 69 |

|    | •    |                                                            |    |

| 3. |      | al RapidlO Electrical Interface                            |    |

|    | 3.1  | Overview                                                   |    |

|    | 3.2  | Port Numbering                                             |    |

|    |      | 3.2.1 Port Configuration                                   |    |

|    | 3.3  | Port Aggregation: 1x and 4x Modes                          |    |

|    |      | 3.3.1 $1x + 1x + 1x + 1x$ Configuration                    |    |

|    |      | 3.3.2 $4x + 0x + 0x + 0x$ Configuration                    |    |

|    | 3.4  | Clocking                                                   |    |

|    |      | 3.4.1 Changing the Link Data Rate                          |    |

|    |      | 3.4.2 Support for Non-standard Baud Rates                  |    |

|    |      | 3.4.3 Changing the Link Data Rate through I <sup>2</sup> C | 79 |

|    | 3.5  | Port Power Down.                                           |    |

|    |      | 3.5.1 Default Configurations on Power Down                 | 80 |

|    |      | 3.5.2 Special Conditions for Port 0 Power Down             | 81 |

|    |      | 3.5.3 Power-Down Options                                   | 81 |

|    |      | 3.5.4 Configuration and Operation Through Power-down       | 82 |

|    | 3.6  | Port Lanes                                                 | 83 |

|    |      | 3.6.1 Lane Synchronization and Alignment                   | 83 |

|    |      | 3.6.2 Lane Swapping                                        | 84 |

|    | 3.7  | Programmable Transmit and Receive Equalization             | 88 |

|    |      | 3.7.1 Transmit Drive Level and Equalization                | 88 |

|    |      | 3.7.2 Receive Equalization                                 | 89 |

|    | 3.8  | Port Loopback Testing                                      | 89 |

|    |      | 3.8.1 Digital Equipment Loopback                           | 90 |

|    |      | 3.8.2 Logical Line Loopback                                | 90 |

|    | 3.9  | Bit Error Rate Testing (BERT)                              | 90 |

|    |      |                                                            |    |

|    |      | 3.9.1    | BERT Pattern Generator                                       | 90  |

|----|------|----------|--------------------------------------------------------------|-----|

|    |      | 3.9.2    | BERT Pattern Matcher and Error Counter                       | 92  |

|    |      | 3.9.3    | Fixed Pattern-based BERT                                     | 92  |

|    |      | 3.9.4    | Using PRBS Scripts for the Transmitters and Receivers        | 93  |

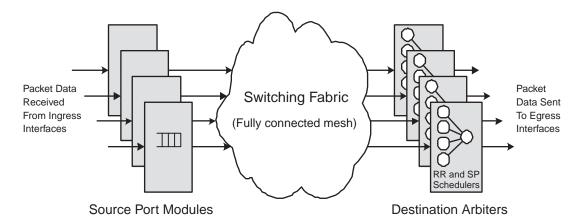

| 4. | Inte | ernal S  | witching Fabric                                              | 95  |

|    | 4.1  | Overvie  | ew                                                           | 95  |

|    | 4.2  | Port Nu  | umbering                                                     | 95  |

|    | 4.3  | Function | onal Behavior                                                | 96  |

|    |      | 4.3.1    | Transfer Modes                                               | 97  |

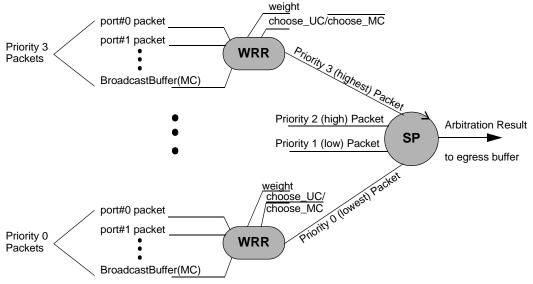

|    | 4.4  | Arbitra  | tion for Egress Port                                         | 98  |

|    |      | 4.4.1    | Strict Priority Arbitration                                  | 99  |

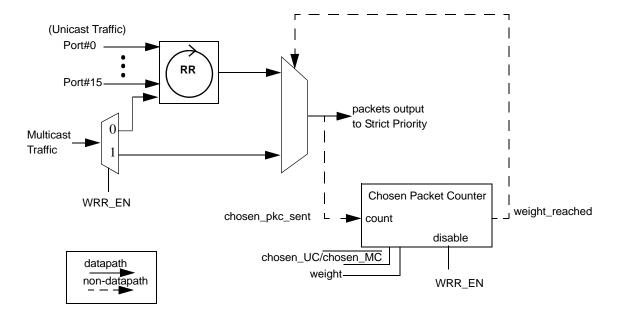

|    |      | 4.4.2    | Weighted Round Robin (WRR) Arbitration                       | 99  |

|    | 4.5  | Packet   | Queuing                                                      | 101 |

|    |      | 4.5.1    | Output Queuing on the Egress Port                            | 101 |

|    |      | 4.5.2    | Input Queue for the ISF Port                                 | 104 |

|    |      | 4.5.3    | Input Arbitration                                            | 105 |

|    |      | 4.5.4    | Input Queuing Model for the Multicast Work Queue             | 109 |

|    |      | 4.5.5    | Input Queuing Model for the Broadcast Buffer                 |     |

|    |      | 4.5.6    | Output Queuing Model for Multicast                           | 110 |

|    |      | 4.5.7    | ISF Bandwidth                                                | 110 |

| _  |      |          |                                                              |     |

| 5. | Mul  | lticast  |                                                              | 111 |

|    | 5.1  | Overvio  | ew                                                           |     |

|    |      | 5.1.1    | Multicast Operation                                          |     |

|    |      | 5.1.2    | Features                                                     | 111 |

|    |      | 5.1.3    | Multicast Operation with Multiple Tsi57x Switches            | 112 |

|    |      | 5.1.4    | Multicast Terminology                                        | 113 |

|    | 5.2  | Multica  | ast Behavior Overview                                        | 113 |

|    |      | 5.2.1    | Multicast Work Queue                                         | 114 |

|    |      | 5.2.2    | Broadcast Buffers                                            | 115 |

|    | 5.3  | Multica  | ast Group Tables                                             | 118 |

|    |      | 5.3.1    | Configuring Basic Associations.                              | 119 |

|    |      | 5.3.2    | Configuring Multicast Masks.                                 | 121 |

|    |      | 5.3.3    | Configuring Multicast Masks Using the IDT Specific Registers | 124 |

|    | 5.4  | Arbitra  | tion for Multicast Engine Ingress Port                       | 125 |

|    | 5.5  | Error M  | Management of Multicast Packets                              | 126 |

|    |      | 5.5.1    | Packet TEA                                                   | 126 |

|    |      | 5.5.2    | Multicast Packet Stomping                                    | 126 |

|    |      | 5.5.3    | Multicast Maximum Latency Timer                              | 127 |

|    |      | 5.5.4    | Multicast Packet Time-To-Live                                | 128 |

|    |      | 5.5.5    | Silent Discard of Packets                                    | 128 |

|    |      | 5.5.6    | Port-writes and Multicast                                    | 128 |

|    | 5.6  | Port Re  | eset                                                         | 129 |

| Eve        | ent Not | tification                                                | 131 |

|------------|---------|-----------------------------------------------------------|-----|

| 6.1        | Overvi  | ew                                                        | 131 |

| 6.2        |         | Summary                                                   |     |

| 6.3        |         | Rate Thresholds                                           |     |

|            | 6.3.1   | Maintaining Packet Flow                                   |     |

| 6.4        | Error S | Stopped State Recovery                                    |     |

|            | 6.4.1   | Error Stopped States                                      |     |

|            | 6.4.2   | Input Error-stopped State.                                |     |

|            | 6.4.3   | Link Error Clearing and Recovery.                         |     |

| 6.5        |         | Capture                                                   |     |

| 6.6        |         | rite Notifications                                        |     |

| 0.0        | 6.6.1   | Destination ID                                            |     |

|            | 6.6.2   | Payload                                                   |     |

|            | 6.6.3   | Servicing Port-writes                                     |     |

|            | 6.6.4   | Port-writes and Hot Insertion/Hot Extraction Notification |     |

|            | 6.6.5   | Port-writes and Multicast.                                |     |

| 6.7        |         | pt Notifications                                          |     |

| 0.7        | 6.7.1   | INT_b Signal                                              |     |

|            | 6.7.2   | Global Interrupt Status Register and Interrupt Handling.  |     |

|            | 6.7.3   | Interrupt Notification and Port-writes                    |     |

| 7.1<br>7.2 |         | ew                                                        |     |

| 7.2        |         | Diagram                                                   |     |

| 7.3<br>7.4 |         | as I <sup>2</sup> C Master                                |     |

| 7.4        | 7.4.1   | Example EEPROM Read and Write                             |     |

|            |         | Master Clock Generation                                   |     |

|            | 7.4.2   |                                                           |     |

|            | 7.4.3   | Master Bus Arbitration                                    |     |

|            | 7.4.4   | Master External Device Addressing                         |     |

|            | 7.4.5   | Master Peripheral Addressing                              |     |

| 7.5        | 7.4.6   | Master Data Transactions                                  |     |

| 7.5        |         | as I <sup>2</sup> C Slave                                 |     |

|            | 7.5.1   | Slave Clock Stretching.                                   |     |

|            | 7.5.2   | Slave Device Addressing.                                  |     |

|            | 7.5.3   | Slave Peripheral Addressing                               |     |

|            | 7.5.4   | External I <sup>2</sup> C Register Map.                   |     |

|            | 7.5.5   | Slave Write Data Transactions.                            |     |

|            | 7.5.6   | Slave Read Data Transactions                              |     |

|            | 7.5.7   | Slave Internal Register Accesses                          |     |

|            | 7.5.8   | Slave Access Examples                                     |     |

|            | 7.5.9   | Resetting the I <sup>2</sup> C Slave Interface            |     |

| 7.6        |         | oxes.                                                     |     |

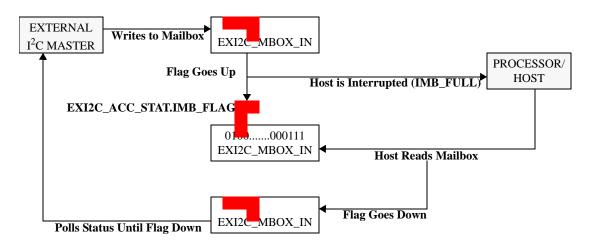

|            | 7.6.1   | Incoming Mailbox                                          |     |

|            | 7.6.2   | Outgoing Mailbox                                          | 175 |

|    | 7.7  |          | Support                                            |     |

|----|------|----------|----------------------------------------------------|-----|

|    |      | 7.7.1    | Unsupported SMBus Features                         |     |

|    |      | 7.7.2    | SMBus Protocol Support                             |     |

|    |      | 7.7.3    | SMBus Alert Response Protocol Support              |     |

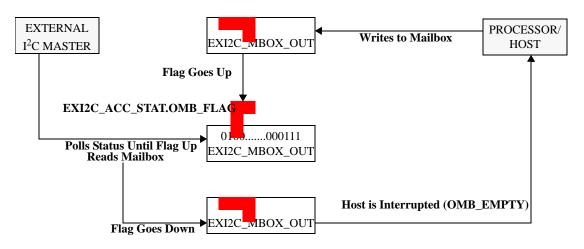

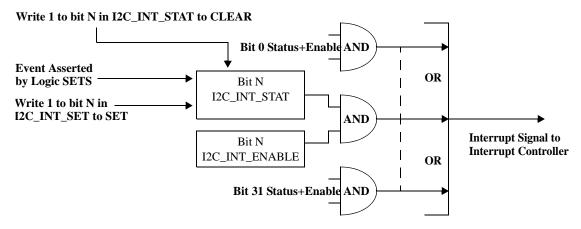

|    | 7.8  | Boot Lo  | pad Sequence                                       | 178 |

|    |      | 7.8.1    | Idle Detect                                        | 180 |

|    |      | 7.8.2    | EEPROM Reset Sequence                              | 180 |

|    |      | 7.8.3    | Wait for Bus Idle                                  | 180 |

|    |      | 7.8.4    | EEPROM Device Detection.                           | 181 |

|    |      | 7.8.5    | Loading Register Data from EEPROM                  | 181 |

|    |      | 7.8.6    | Chaining                                           | 182 |

|    |      | 7.8.7    | EEPROM Data Format                                 | 182 |

|    |      | 7.8.8    | I2C Boot Time                                      | 184 |

|    |      | 7.8.9    | Accelerating Boot Load                             | 185 |

|    | 7.9  | Error H  | andling                                            | 186 |

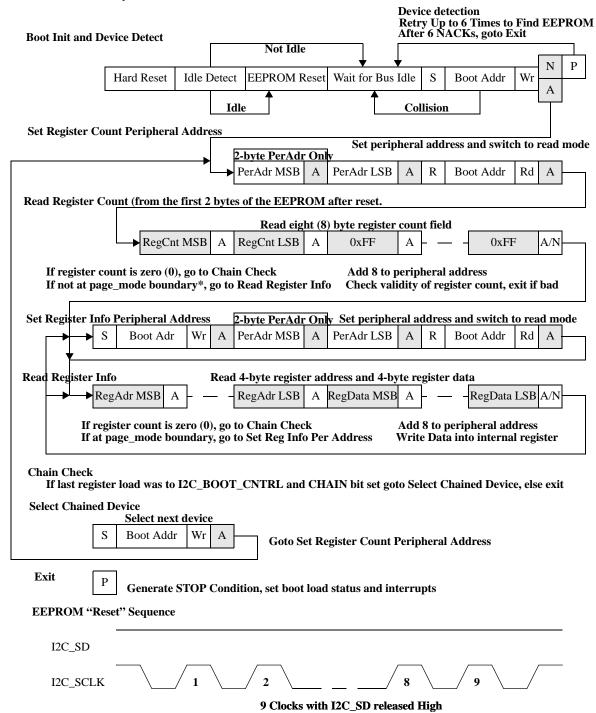

|    | 7.10 |          | ot Handling                                        |     |

|    | 7.11 | Events   | versus Interrupts                                  | 189 |

|    | 7.12 |          | its                                                |     |

|    | 7.13 |          | ning                                               |     |

|    |      | 7.13.1   | Start/Restart Condition Setup and Hold             |     |

|    |      | 7.13.2   | Stop Condition Setup                               |     |

|    |      | 7.13.3   | I2C_SD Setup and Hold                              |     |

|    |      | 7.13.4   | I2C_SCLK Nominal and Minimum Periods               |     |

|    |      | 7.13.5   | Idle Detect Period.                                |     |

|    |      | ,,,,,,,, | 200001000000000000000000000000000000000            |     |

| 8. | Per  | formar   | 1Ce                                                | 199 |

|    | 8.1  | Overvie  | ew                                                 | 199 |

|    |      | 8.1.1    | Throughput                                         | 199 |

|    |      | 8.1.2    | Latency                                            | 199 |

|    | 8.2  | Perform  | nance Monitoring                                   |     |

|    |      | 8.2.1    | Traffic Efficiency                                 |     |

|    |      | 8.2.2    | Throughput                                         |     |

|    |      | 8.2.3    | Bottleneck Detection                               |     |

|    |      | 8.2.4    | Congestion Detection                               |     |

|    |      | 8.2.5    | Resetting Performance Registers                    |     |

|    | 8.3  |          | uring the Tsi577 for Performance Measurements      |     |

|    | 0.5  | 8.3.1    | Clock Speeds                                       |     |

|    |      | 8.3.2    | Tsi577 ISF Arbitration Settings                    |     |

|    |      | 8.3.3    | Tsi577 RapidIO Transmission Scheduler Settings.    |     |

|    |      | 8.3.4    | •                                                  |     |

|    | 0.4  |          | Tsi577 RapidIO Buffer Watermark Selection Settings |     |

|    | 8.4  |          | Port Performance Characteristics                   |     |

|    |      | 8.4.1    | Port-to-Port Packet Latency Performance            |     |

|    |      | 8.4.2    | Packet Throughput Performance                      |     |

|    | 0.5  | 8.4.3    | Multicast Performance                              |     |

|    | 8.5  | •        | tion Detection and Management                      |     |

|    |      | 8.5.1    | Congestion Registers                               | 211 |

| 9.  | JTA  | G Inte  | rface                                               | 215 |

|-----|------|---------|-----------------------------------------------------|-----|

|     | 9.1  | Overvie | ew                                                  | 215 |

|     | 9.2  |         | Device Identification Number                        |     |

|     | 9.3  |         | Register Access Details                             |     |

|     |      | 9.3.1   | Format                                              |     |

|     |      | 9.3.2   | Write Access to Registers from the JTAG Interface   |     |

|     |      | 9.3.3   | Read Access to Registers from the JTAG Interface    |     |

| 10. | Clo  | cks, R  | esets and Power-up Options                          | 219 |

|     | 10.1 |         |                                                     |     |

|     |      | 10.1.1  | Clocking Architecture                               |     |

|     |      | 10.1.2  | SerDes Clocks                                       |     |

|     |      | 10.1.3  | Clock Domains                                       |     |

|     |      | 10.1.4  | Clock Gating                                        |     |

|     | 10.2 |         | elota emmig                                         |     |

|     | 10.2 | 10.2.1  | Device Reset                                        |     |

|     |      | 10.2.2  | Per-Port Reset                                      |     |

|     |      | 10.2.3  | Generating a RapidIO Reset Request to a Peer Device |     |

|     |      | 10.2.4  | JTAG Reset                                          |     |

|     | 10.3 |         | up Options                                          |     |

|     |      | 10.3.1  | Power-up Option Signals                             |     |

|     |      | 10.3.2  | Default Port Speed                                  |     |

|     |      | 10.3.3  | Port Power-up and Power-down                        |     |

|     |      | 10.3.4  | Port Width Override                                 | 230 |

| 11. | Sigi | nals    |                                                     | 231 |

|     | 11.1 |         | ew                                                  |     |

|     | 11.2 |         | Ordering.                                           |     |

|     | 11.3 |         | Grouping                                            |     |

|     | 11.4 | _       | Compatibility Modes                                 |     |

|     | 11.5 |         | and Ballmap                                         |     |

| 12. | Seri | ial Ran | pidIO Registers                                     | 245 |

|     | 12.1 | -       | ew                                                  |     |

|     |      | 12.1.1  | Reserved Register Addresses and Fields              |     |

|     | 12.2 |         | umbering                                            |     |

|     | 12.3 |         | ntions                                              |     |

|     | 12.4 |         | er Map                                              |     |

|     | 12.5 | _       | O Logical Layer and Transport Layer Registers.      |     |

|     | 12.0 | 12.5.1  | RIO Device Identity CAR                             |     |

|     |      | 12.5.2  | RIO Device Information CAR.                         |     |

|     |      | 12.5.3  | RIO Assembly Identity CAR.                          |     |

|     |      | 12.5.4  | RIO Assembly Information CAR                        |     |

|     |      | 12.5.5  | RIO Processing Element Features CAR                 |     |

|     |      | 12.5.6  | RIO Switch Port Information CAR                     |     |

|     |      | 12.5.7  | RIO Source Operation CAR                            |     |

|     |      |         |                                                     |     |

|      | 12.5.8  | RIO Switch Multicast Support CAR                                                 | 273 |

|------|---------|----------------------------------------------------------------------------------|-----|

|      | 12.5.9  | RIO Route LUT Size CAR                                                           | 274 |

|      | 12.5.10 | RIO Switch Multicast Information CAR                                             | 275 |

|      | 12.5.11 | RIO Host Base Device ID Lock CSR                                                 | 276 |

|      | 12.5.12 | RIO Component Tag CSR                                                            | 277 |

|      | 12.5.13 | RIO Route Configuration DestID CSR                                               | 278 |

|      | 12.5.14 | RIO Route Configuration Output Port CSR                                          | 279 |

|      | 12.5.15 | RIO Route LUT Attributes (Default Port) CSR                                      | 280 |

|      | 12.5.16 | RIO Multicast Mask Configuration Register                                        | 281 |

|      | 12.5.17 | RIO Multicast DestID Configuration Register                                      | 283 |

|      | 12.5.18 | RIO Multicast DestID Association Register                                        | 284 |

| 12.6 | RapidIO | Physical Layer Registers                                                         | 286 |

|      | 12.6.1  | RIO 1x or 4x Switch Port Maintenance Block Header                                | 288 |

|      | 12.6.2  | RIO Switch Port Link Time Out Control CSR                                        | 289 |

|      | 12.6.3  | RIO Switch Port General Control CSR                                              | 290 |

|      | 12.6.4  | RIO Serial Port x Link Maintenance Request CSR                                   | 291 |

|      | 12.6.5  | RIO Serial Port x Link Maintenance Response CSR                                  | 292 |

|      | 12.6.6  | RIO Serial Port x Local ackID Status CSR                                         | 293 |

|      | 12.6.7  | RIO Port x Error and Status CSR                                                  | 295 |

|      | 12.6.8  | RIO Serial Port x Control CSR                                                    | 298 |

| 12.7 | RapidIO | Error Management Extension Registers                                             | 302 |

|      | 12.7.1  | Port Behavior When Error Rate Failed Threshold is Reached                        | 303 |

|      | 12.7.2  | RIO Error Reporting Block Header                                                 | 304 |

|      | 12.7.3  | RapidIO Logical and Transport Layer Error Detect CSR                             | 305 |

|      | 12.7.4  | RapidIO Logical and Transport Layer Error Enable CSR                             | 306 |

|      | 12.7.5  | RapidIO Logical and Transport Layer Address Capture CSR                          | 307 |

|      | 12.7.6  | RapidIO Logical and Transport Layer Device ID Capture CSR                        | 308 |

|      | 12.7.7  | RapidIO Logical and Transport Layer Control Capture CSR                          | 309 |

|      | 12.7.8  | RIO Port-Write Target Device ID CSR                                              | 310 |

|      | 12.7.9  | RIO Packet Time-to Live CSR                                                      | 311 |

|      | 12.7.10 | RIO Port x Error Detect CSR                                                      | 312 |

|      | 12.7.11 | RIO Port x Error Rate Enable CSR                                                 | 315 |

|      | 12.7.12 | RIO Port x Error Capture Attributes CSR and Debug 0                              |     |

|      | 12.7.13 | RIO Port x Packet and Control Symbol Error Capture CSR 0 and Debug 1             | 319 |

|      | 12.7.14 | RIO Port x Packet Error Capture CSR 1 and Debug 2                                | 320 |

|      | 12.7.15 | RIO Port x Packet Error Capture CSR 2 and Debug 3                                | 321 |

|      | 12.7.16 | RIO Port x Packet Error Capture CSR 3 and Debug 4                                | 322 |

|      | 12.7.17 | RIO Port x Error Rate CSR                                                        | 323 |

|      | 12.7.18 | RIO Port x Error Rate Threshold CSR                                              | 325 |

| 12.8 | IDT-Spe | cific RapidIO Registers                                                          | 326 |

|      | 12.8.1  | RIO Port x Discovery Timer                                                       | 328 |

|      | 12.8.2  | RIO Port x Mode CSR                                                              | 329 |

|      | 12.8.3  | RIO Port x Multicast-Event Control Symbol and Reset Control Symbol Interrupt CSR | 331 |

|      | 12.8.4  | RIO Port x RapidIO Watermarks                                                    | 332 |

|      | 12.8.5  | RIO Port x Route Config DestID CSR                                               | 333 |

|       | 12.8.6    | RIO Port x Route Config Output Port CSR                            | 334 |

|-------|-----------|--------------------------------------------------------------------|-----|

|       | 12.8.7    | RIO Port x Local Routing LUT Base CSR                              | 335 |

|       | 12.8.8    | RIO Multicast Write ID x Register                                  | 336 |

|       | 12.8.9    | RIO Multicast Write Mask x Register                                | 337 |

|       | 12.8.10   | RIO Port x Control Independent Register                            | 338 |

|       | 12.8.11   | RIO Port x Send Multicast-Event Control Symbol Register            | 341 |

|       | 12.8.12   | RIO Port x LUT Parity Error Info CSR                               | 342 |

|       | 12.8.13   | RIO Port x Control Symbol Transmit                                 | 344 |

|       | 12.8.14   | RIO Port x Interrupt Status Register                               | 345 |

|       | 12.8.15   | RIO Port x Interrupt Generate Register                             | 349 |

| 12.9  | IDT-Spec  | cific Performance Registers                                        | 351 |

|       | 12.9.1    | RIO Port x Performance Statistics Counter 0 and 1 Control Register | 352 |

|       | 12.9.2    | RIO Port x Performance Statistics Counter 2 and 3 Control Register | 356 |

|       | 12.9.3    | RIO Port x Performance Statistics Counter 4 and 5 Control Register | 360 |

|       | 12.9.4    | RIO Port x Performance Statistics Counter 0 Register               | 364 |

|       | 12.9.5    | RIO Port x Performance Statistics Counter 1 Register               | 365 |

|       | 12.9.6    | RIO Port x Performance Statistics Counter 2 Register               | 366 |

|       | 12.9.7    | RIO Port x Performance Statistics Counter 3 Register               | 367 |

|       | 12.9.8    | RIO Port x Performance Statistics Counter 4 Register               | 368 |

|       | 12.9.9    | RIO Port x Performance Statistics Counter 5 Register               | 369 |

|       | 12.9.10   | RIO Port x Transmitter Output Queue Depth Threshold Register       | 370 |

|       | 12.9.11   | RIO Port x Transmitter Output Queue Congestion Status Register     | 373 |

|       | 12.9.12   | RIO Port x Transmitter Output Queue Congestion Period Register     | 374 |

|       | 12.9.13   | RIO Port x Receiver Input Queue Depth Threshold Register           | 376 |

|       | 12.9.14   | RIO Port x Receiver Input Queue Congestion Status Register         | 378 |

|       | 12.9.15   | RIO Port x Receiver Input Queue Congestion Period Register         | 379 |

|       | 12.9.16   | RIO Port x Reordering Counter Register                             | 381 |

| 12.10 | Serial Po | ort Electrical Layer Registers                                     | 382 |

|       | 12.10.1   | BYPASS_INIT Functionality                                          | 383 |

|       | 12.10.2   | SRIO MAC x SerDes Configuration Channel 0                          | 384 |

|       | 12.10.3   | SRIO MAC x SerDes Configuration Channel 1                          | 387 |

|       | 12.10.4   | SRIO MAC x SerDes Configuration Channel 2                          | 390 |

|       | 12.10.5   | SRIO MAC x SerDes Configuration Channel 3                          | 393 |

|       | 12.10.6   | SRIO MAC x SerDes Configuration Global                             | 396 |

|       | 12.10.7   | SRIO MAC x SerDes Configuration GlobalB                            | 400 |

|       | 12.10.8   | SRIO MAC x Digital Loopback and Clock Selection Register           | 401 |

|       | 12.10.9   | RIO Serial MAC SerDes Output Pins Register                         | 406 |

| 12.11 | Per Port  | Copies of Global Registers                                         | 408 |

|       | 12.11.1   | RapidIO Serial Port x Multicast Write ID 0                         | 408 |

|       | 12.11.2   | RapidIO Serial Port x Multicast Write ID 1                         | 409 |

|       | 12.11.3   | RapidIO Serial Port x Multicast Write ID 2                         | 410 |

|       | 12.11.4   | RapidIO Serial Port x Multicast Write ID 3                         | 411 |

|       | 12.11.5   | RapidIO Serial Port x Multicast Write ID 4                         | 412 |

|       | 12.11.6   | RapidIO Serial Port x Multicast Write ID 5                         |     |

|       | 12.11.7   | RapidIO Serial Port x Multicast Write ID 6                         | 414 |

|       | 12.11.8    | RapidIO Serial Port x Multicast Write ID 7                         | 415 |

|-------|------------|--------------------------------------------------------------------|-----|

|       | 12.11.9    | RapidIO Serial Port x Switch Port Link Timeout Control CSR         | 416 |

|       | 12.11.10   | RapidIO Serial Port x Port Write Target Device ID CSR              | 417 |

|       | 12.11.11   | RapidIO Serial Port x Packet Time-to Live CSR                      | 418 |

|       | 12.11.12   | RapidIO Serial Port x Switch Port General Control CSR              | 419 |

|       | 12.11.13   | RapidIO Serial Port x Component Tag CSR                            | 420 |

|       | 12.11.14   | RapidIO Serial Port x Route LUT Attributes (Default Port) CSR      | 421 |

|       |            | RapidIO Serial Port x Logical and Transport Layer Error Enable CSR |     |

| 12.12 | Internal S | Switching Fabric (ISF) Registers                                   | 423 |

|       | 12.12.1    | Fabric Control Register                                            | 423 |

|       | 12.12.2    | Fabric Interrupt Status Register                                   | 425 |

|       | 12.12.3    | RIO Broadcast Buffer Maximum Latency Expired Error Register        | 427 |

|       | 12.12.4    | RIO Broadcast Buffer Maximum Latency Expired Override              | 429 |

| 12.13 | Utility U  | nit Registers                                                      | 431 |

|       | 12.13.1    | Global Interrupt Status Register                                   | 431 |

|       | 12.13.2    | Global Interrupt Enable Register                                   | 433 |

|       | 12.13.3    | Global Power-up Status Register                                    | 435 |

|       | 12.13.4    | RIO Port-Write Timeout Control Register                            | 436 |

|       | 12.13.5    | RIO Port Write Outstanding Request Register                        | 437 |

|       | 12.13.6    | MCES Pin Control Register                                          | 438 |

| 12.14 | Multicast  | t Registers                                                        | 439 |

|       | 12.14.1    | RIO Multicast Register Version CSR                                 | 439 |

|       | 12.14.2    | RIO Multicast Maximum Latency Counter CSR                          | 440 |

|       | 12.14.3    | RIO Port x ISF Watermarks                                          | 441 |

|       | 12.14.4    | Port x Prefer Unicast and Multicast Packet Prio 0 Register         | 442 |

|       | 12.14.5    | Port x Prefer Unicast and Multicast Packet Prio 1 Register         | 443 |

|       | 12.14.6    | Port x Prefer Unicast and Multicast Packet Prio 2 Register         | 444 |

|       | 12.14.7    | Port x Prefer Unicast and Multicast Packet Prio 3 Register         | 445 |

| 12.15 | SerDes P   | er Lane Register                                                   | 446 |

|       | 12.15.1    | SerDes N Lane 0 Pattern Generator Control Register                 | 447 |

|       | 12.15.2    | SerDes N Lane 0 Pattern Matcher Control Register                   | 448 |

|       | 12.15.3    | SerDes N Lane 0 Frequency and Phase Value Register                 | 450 |

|       | 12.15.4    | SerDes N Lane 1 Pattern Generator Control Register                 | 451 |

|       | 12.15.5    | SerDes N Lane 1 Pattern Matcher Control Register                   | 452 |

|       | 12.15.6    | SerDes N Lane 1 Frequency and Phase Value Register                 | 454 |

|       | 12.15.7    | SerDes N Lane 2 Pattern Generator Control Register                 | 455 |

|       | 12.15.8    | SerDes N Lane 2 Pattern Matcher Control Register                   | 456 |

|       | 12.15.9    | SerDes N Lane 2 Frequency and Phase Value Register                 | 458 |

|       | 12.15.10   | SerDes N Lane 3 Pattern Generator Control Register                 | 459 |

|       | 12.15.11   | SerDes N Lane 3 Pattern Matcher Control Register                   | 460 |

|       | 12.15.12   | SerDes N Lane 3 Frequency and Phase Value Register                 | 462 |

| I2C I | Registe    | ers                                                                | 463 |

| 13.1  | _          | Map                                                                |     |

| 13.2  | · ·        | Descriptions                                                       |     |

|       | 13.2.1     | I <sup>2</sup> C Device ID Register                                |     |

|       |            |                                                                    |     |

**13.**

|    |      | 13.2.2   | I <sup>2</sup> C Reset Register                                      | . 467 |

|----|------|----------|----------------------------------------------------------------------|-------|

|    |      | 13.2.3   | I <sup>2</sup> C Master Configuration Register                       | . 468 |

|    |      | 13.2.4   | I <sup>2</sup> C Master Control Register                             | . 470 |

|    |      | 13.2.5   | I <sup>2</sup> C Master Receive Data Register                        | . 473 |

|    |      | 13.2.6   | I <sup>2</sup> C Master Transmit Data Register                       | . 474 |

|    |      | 13.2.7   | I <sup>2</sup> C Access Status Register                              | . 475 |

|    |      | 13.2.8   | I <sup>2</sup> C Interrupt Status Register                           | . 478 |

|    |      | 13.2.9   | I <sup>2</sup> C Interrupt Enable Register                           | . 481 |

|    |      | 13.2.10  | I <sup>2</sup> C Interrupt Set Register                              | . 483 |

|    |      | 13.2.11  | I <sup>2</sup> C Slave Configuration Register                        | . 485 |

|    |      | 13.2.12  | I <sup>2</sup> C Boot Control Register                               | . 488 |

|    |      | 13.2.13  | Externally Visible I <sup>2</sup> C Internal Write Address Register  | . 492 |

|    |      | 13.2.14  | Externally Visible I <sup>2</sup> C Internal Write Data Register     | . 493 |

|    |      | 13.2.15  | Externally Visible I <sup>2</sup> C Internal Read Address Register   | . 494 |

|    |      | 13.2.16  | Externally Visible I <sup>2</sup> C Internal Read Data Register      | . 495 |

|    |      | 13.2.17  | Externally Visible I <sup>2</sup> C Slave Access Status Register     | . 496 |

|    |      | 13.2.18  | Externally Visible I <sup>2</sup> C Internal Access Control Register | . 498 |

|    |      | 13.2.19  | Externally Visible I <sup>2</sup> C Status Register                  | . 500 |

|    |      | 13.2.20  | Externally Visible I <sup>2</sup> C Enable Register                  | . 504 |

|    |      | 13.2.21  | Externally Visible I <sup>2</sup> C Outgoing Mailbox Register        | . 508 |

|    |      | 13.2.22  | Externally Visible I <sup>2</sup> C Incoming Mailbox Register        | . 509 |

|    |      | 13.2.23  | I <sup>2</sup> C Event and Event Snapshot Registers                  | . 510 |

|    |      | 13.2.24  | I <sup>2</sup> C New Event Register                                  | . 514 |

|    |      | 13.2.25  | I <sup>2</sup> C Enable Event Register                               | . 517 |

|    |      | 13.2.26  | I <sup>2</sup> C Time Period Divider Register                        | . 520 |

|    |      | 13.2.27  | I <sup>2</sup> C Start Condition Setup/Hold Timing Register          | . 521 |

|    |      | 13.2.28  | I <sup>2</sup> C Stop/Idle Timing Register                           | . 522 |

|    |      | 13.2.29  | I2C_SD Setup and Hold Timing Register                                | . 523 |

|    |      | 13.2.30  | I2C_SCLK High and Low Timing Register                                | . 524 |

|    |      | 13.2.31  | I2C_SCLK Minimum High and Low Timing Register                        | . 525 |

|    |      | 13.2.32  | I2C_SCLK Low and Arbitration Timeout Register                        | . 526 |

|    |      | 13.2.33  | I <sup>2</sup> C Byte/Transaction Timeout Register                   | . 527 |

|    |      | 13.2.34  | I <sup>2</sup> C Boot and Diagnostic Timer                           | . 528 |

|    |      |          | I <sup>2</sup> C Boot Load Diagnostic Progress Register              |       |

|    |      | 13.2.36  | I <sup>2</sup> C Boot Load Diagnostic Configuration Register         | . 530 |

| ۹. | Seri | al Rapi  | dIO Protocol Overview                                                | 531   |

|    | A.1  | Protocol |                                                                      | . 531 |

|    | A.2  | Packets. |                                                                      | . 531 |

|    |      | A.2.1    | Control Symbols                                                      | . 532 |

|    | A.3  | Physical | Layer                                                                | . 532 |

|    |      | A.3.1    | PCS Layer                                                            | . 532 |

|    |      | A.3.2    | PMA Layer                                                            | . 532 |

|    |      | A.3.3    | Physical Protocol                                                    | . 532 |

|    |      |          |                                                                      |       |

| B.   | PRBS Scripts 537 |                                  |       |  |  |

|------|------------------|----------------------------------|-------|--|--|

|      | B.1              | Tsi577_start_prbs_all.txt Script | . 537 |  |  |

|      | B.2              | Tsi577_framer_disable.txt Script | . 538 |  |  |

|      | B.3              | Tsi577_sync_prbs_all.txt Script  | . 539 |  |  |

|      | B.4              | Tsi577_read_prbs_all.txt Script  | . 541 |  |  |

| Inde | ex               |                                  | 543   |  |  |

## **Figures**

| Figure 1:  | Tsi577 Block Diagram                                         | 24    |

|------------|--------------------------------------------------------------|-------|

| Figure 2:  | Wireless Baseband Card                                       | 25    |

| Figure 3:  | Video Infrastructure Card                                    | 25    |

| Figure 4:  | Tsi577 MAC Block Diagram                                     | 32    |

| Figure 5:  | LUT Mode of Operation                                        | 43    |

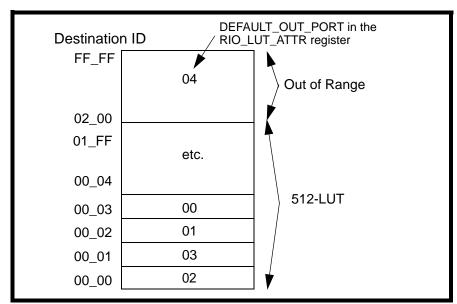

| Figure 6:  | Flat Mode Routing                                            | 45    |

| Figure 7:  | Flat Mode Routing Example                                    | 46    |

| Figure 8:  | Flat Mode LUT Configuration Example                          | 47    |

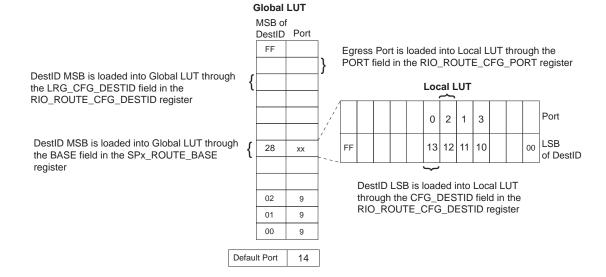

| Figure 9:  | Hierarchical Mode                                            | 50    |

| Figure 10: | Hierarchical Mode Routing Example                            | 51    |

| Figure 11: | LOLS Silent Period                                           | 68    |

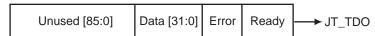

| Figure 12: | Tsi577 MAC Block Diagram                                     | 73    |

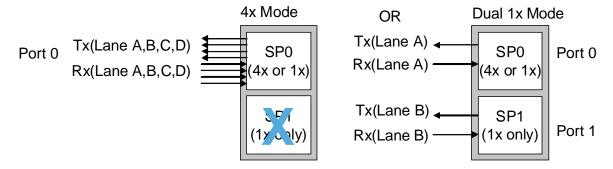

| Figure 13: | Port Configuration                                           | 75    |

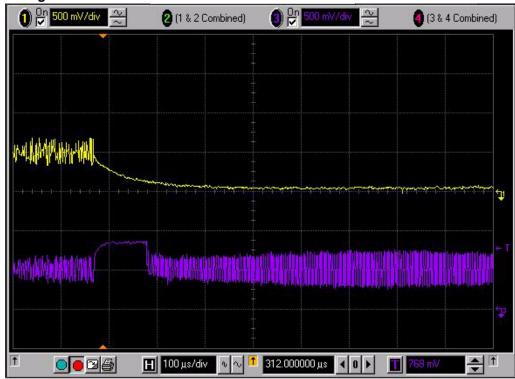

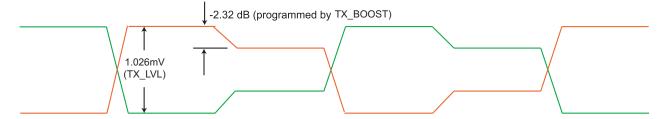

| Figure 14: | Drive Strength and Equalization Waveform                     | 88    |

| Figure 15: | Tsi577 Loopbacks                                             | 89    |

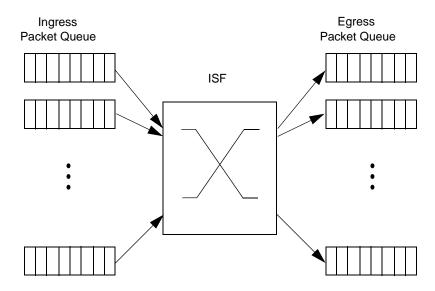

| Figure 16: | ISF Block Diagram                                            | 97    |

| Figure 17: | Egress Arbitration: Weighted Round Robin and Strict Priority | 98    |

| Figure 18: | Weighted Round Robin Arbiter per Priority Group              | 99    |

| Figure 19: | Ingress and Egress Packet Queues in Tsi577                   | . 101 |

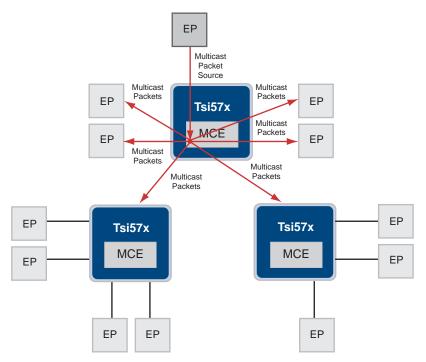

| Figure 20: | Multicast Operation – Option 1                               | . 112 |

| Figure 21: | Multicast Operation – Option 2                               | . 113 |

| Figure 22: | Multicast Packet Flow in the Tsi577                          | . 116 |

| Figure 23: | Relationship Representation                                  | . 119 |

| Figure 24: | Completed Tables at the End of Configuration                 | . 122 |

| Figure 25: | IDT-specific Multicast Mask Configuration                    | . 125 |

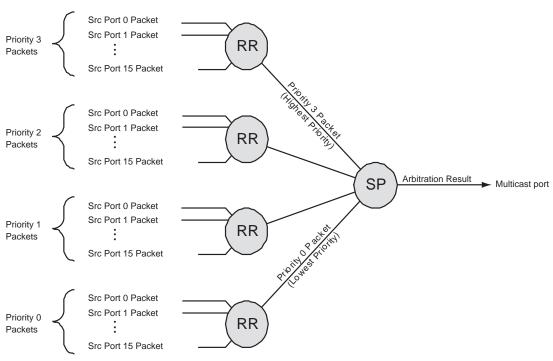

| Figure 26: | Arbitration Algorithm for Multicast Port                     | . 126 |

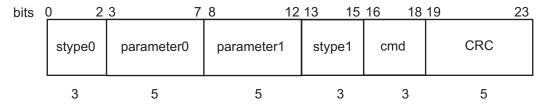

| Figure 27: | Control Symbol Format                                        | . 141 |

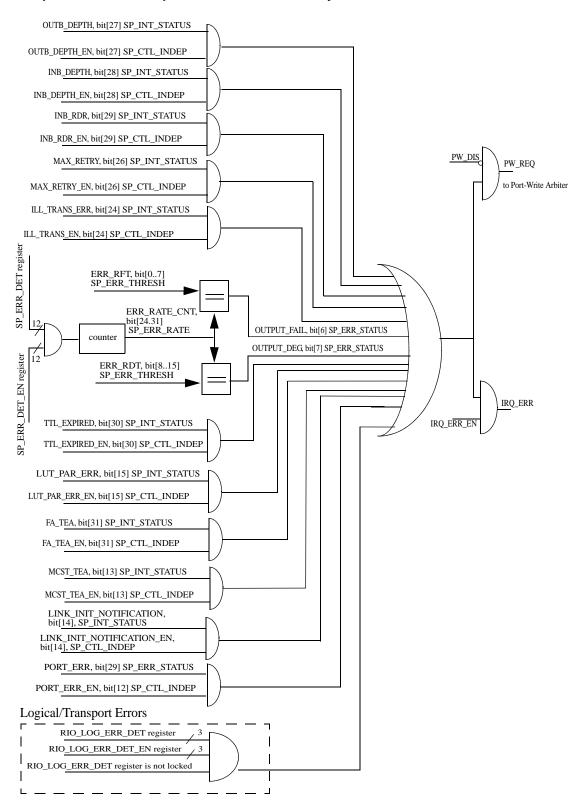

| Figure 28: | RapidIO Block Interrupt and Port Write Hierarchy             | . 148 |

| Figure 29: | Global Interrupt generation                                  | . 149 |

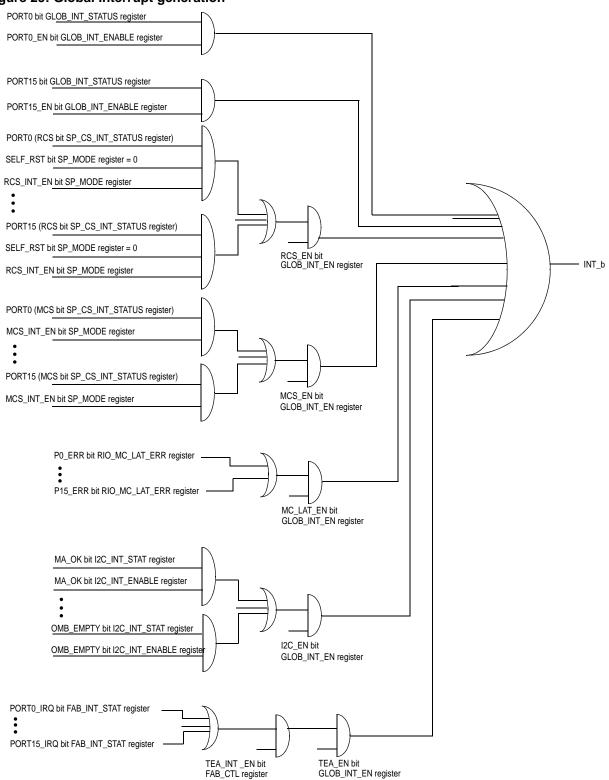

| Figure 30: | I <sup>2</sup> C Block Diagram                               | . 157 |

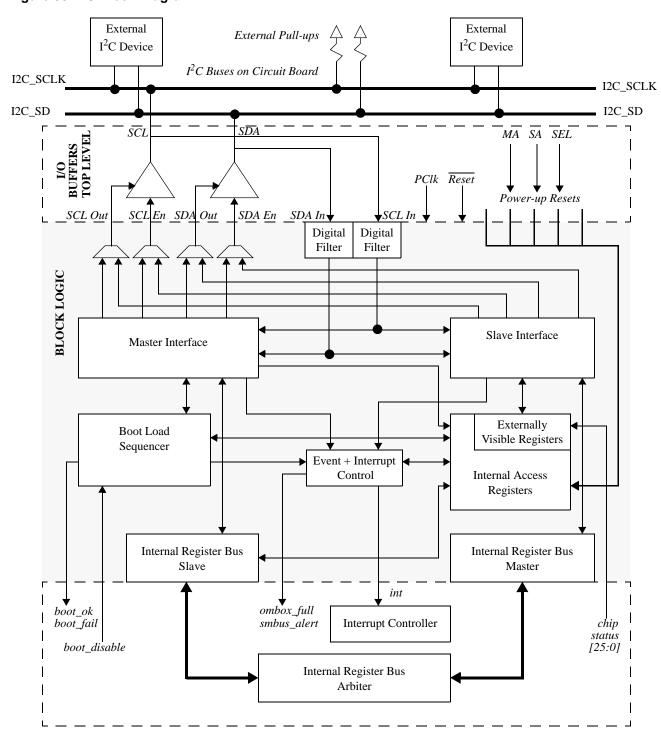

| Figure 31: | I <sup>2</sup> C Reference Diagram                           | . 158 |

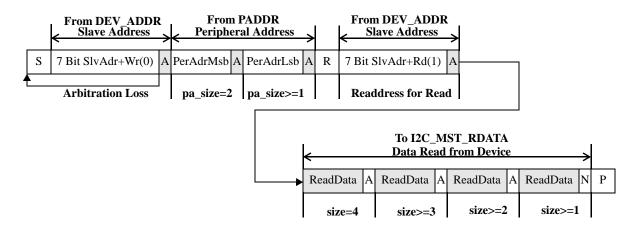

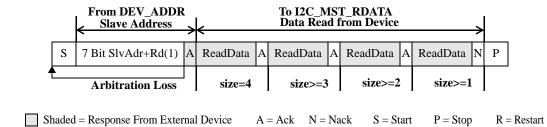

| Figure 32: | Software-initiated Master Transactions                       | . 160 |

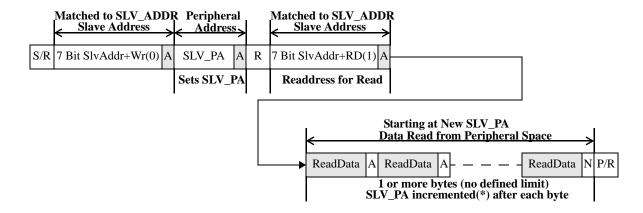

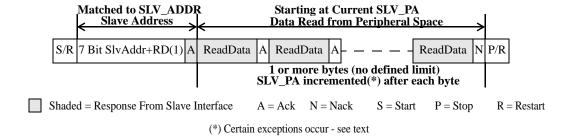

| Figure 33: | Transaction Protocols for Tsi577 as Slave                    | . 165 |

| Figure 34: | I <sup>2</sup> C Mailbox Operation                           | . 174 |

| Figure 35: | SMBus Protocol Support                                       | . 177 |

| Figure 36: | SMBus Alert Response Protocol.                               | . 178 |

| Figure 37: | Boot Load Sequence                                           | . 179 |

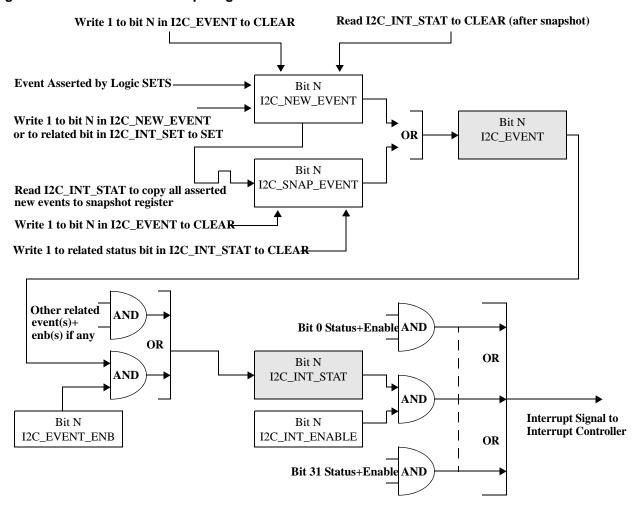

| Figure 38: | I <sup>2</sup> C Interrupt Generation                        |       |

| Figure 39: | I <sup>2</sup> C Event and Interrupt Logic                   |       |

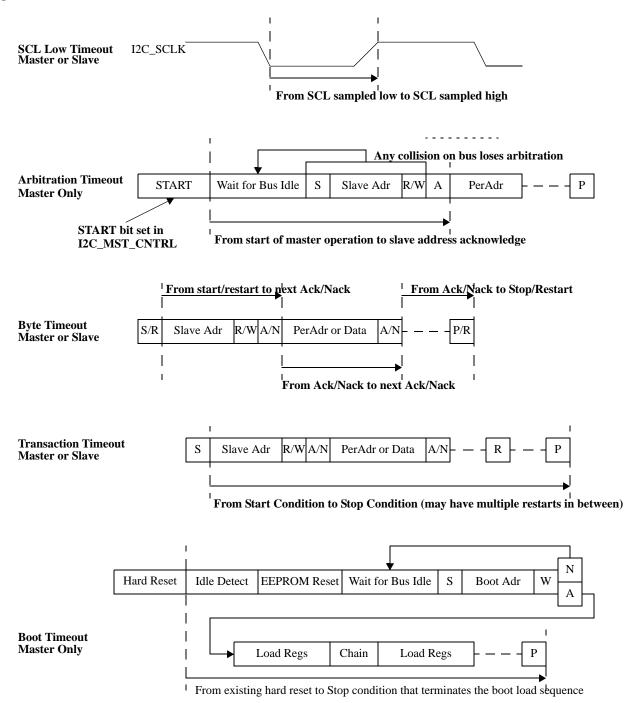

| Figure 40: | I <sup>2</sup> C Timeout Periods                             |       |

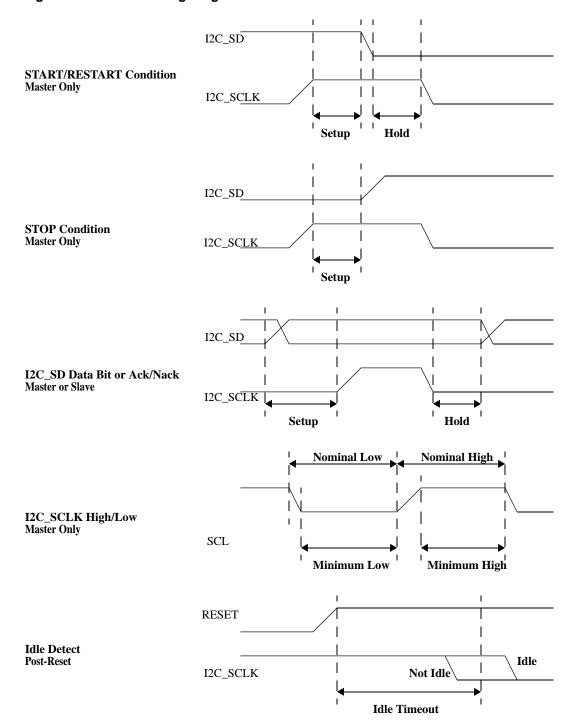

| Figure 41: | I <sup>2</sup> C Bus Timing Diagrams                         | . 196 |

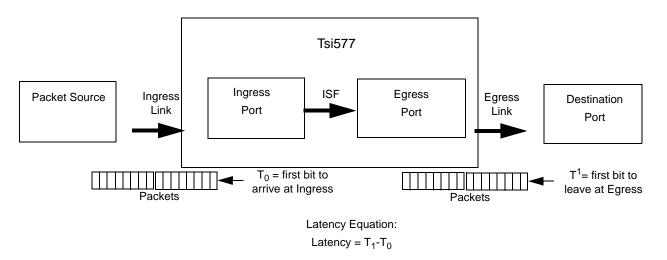

| Figure 42: | Latency Illustration                                         | . 200 |

16 Figures

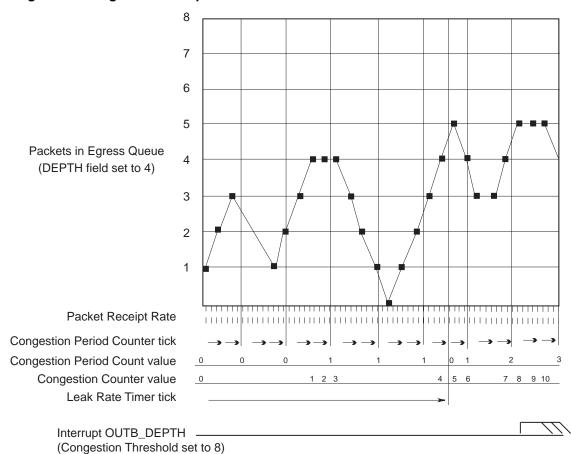

| Figure 43: | Congestion and Detection Flowchart          | 210 |

|------------|---------------------------------------------|-----|

| Figure 44: | Congestion Example                          | 213 |

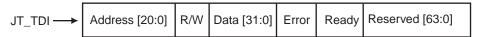

| Figure 45: | Register Access From JTAG - Serial Data In  | 216 |

| Figure 46: | Register Access From JTAG - Serial Data Out | 216 |

| Figure 47: | Clock Architecture                          | 221 |

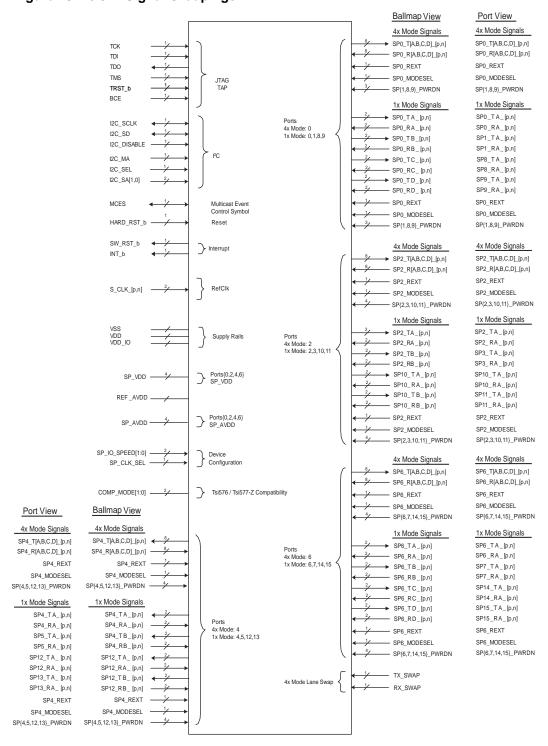

| Figure 48: | Tsi577 Signal Groupings                     | 233 |

## **Tables**

| Table 1:  | Tsi577 MAC Serial RapidIO Port Assignment                                          | 31  |

|-----------|------------------------------------------------------------------------------------|-----|

| Table 2:  | Tsi577 Port Numbering                                                              | 37  |

| Table 3:  | Error Summary                                                                      | 53  |

| Table 4:  | Lookup Table States                                                                | 55  |

| Table 5:  | Examples of Maintenance Packets with Hop count = 0 and Associated Tsi577 Responses | 57  |

| Table 6:  | TTL Behavior of Unicast Packets in the Tsi577                                      | 62  |

| Table 7:  | TTL Behavior of Multicast Packets in the Tsi577                                    | 62  |

| Table 8:  | Tsi577 MAC Serial RapidIO Port Assignment                                          | 71  |

| Table 9:  | Tsi577 Port Numbering                                                              | 74  |

| Table 10: | Reference Clock Frequency and Supported RapidIO Data Rates                         | 77  |

| Table 11: | Non-standard Baud Rates                                                            |     |

| Table 12: | Serial Port Power Down Procedure                                                   | 82  |

| Table 13: | 1x Mode SPx/Channel and Lane Numbering                                             | 85  |

| Table 14: | 4x Mode SPx/Channel and Lane Numbering.                                            | 86  |

| Table 15: | 4x Mode SPx/Channel and Lane Numbering When Lanes are Swapped                      | 87  |

| Table 16: | Patterns Supported by Generator                                                    | 90  |

| Table 17: | Patterns Supported by Matcher                                                      |     |

| Table 18: | Switch ISF Port Numbering                                                          |     |

| Table 19: | Sample Register settings for WRR in a given priority group (WRR_EN=1)              |     |

| Table 20: | Examples of Use of Watermarks                                                      |     |

| Table 21: | Multicast Terminology                                                              | 113 |

| Table 22: | Tsi577 Events                                                                      | 132 |

| Table 23: | Error Rate Error Events                                                            | 143 |

| Table 24: | Port Write Packet Data Payload — Error Reporting                                   | 146 |

| Table 25: | Externally Visible I <sup>2</sup> C Register Map                                   | 167 |

| Table 26: | Format for Boot Loadable EEPROM                                                    |     |

| Table 27: | Sample EEPROM Loading Two Registers                                                | 183 |

| Table 28: | Sample EEPROM With Chaining                                                        |     |

| Table 29: | I <sup>2</sup> C Error Handling                                                    | 186 |

| Table 30: | I <sup>2</sup> C Interrupt to Events Mapping                                       | 190 |

| Table 31: | Performance Monitoring Parameters                                                  |     |

| Table 32: | 4x/1x Latency Numbers Under No Congestion                                          | 206 |

| Table 33: | 4x/1x Multicast Latency Numbers Under No Congestion                                | 208 |

| Table 34: | Input Clock Signals                                                                | 219 |

| Table 35: | Bi-direct I <sup>2</sup> C Clock Signal                                            | 220 |

| Table 36: | Clock Domains.                                                                     |     |

| Table 37: | Power-up Options Signals                                                           | 227 |

| Table 38: | Signal Types                                                                       | 231 |

| Table 39: | Signal Descriptions and Recommended Termination                                    | 234 |

| Table 40: | Tsi577 Compatibility Modes                                                         | 243 |

| Table 41: | List of Tsi577 Compatibility Modes                                                 |     |

| Table 42: | Address Rules.                                                                     | 245 |

18 Tables

| Table 43: | Register Access Types                         | . 246 |

|-----------|-----------------------------------------------|-------|

| Table 44: | Tsi577 Port Numbering                         | . 247 |

| Table 45: | Register map overview                         | . 250 |

| Table 46: | Register Map                                  | . 251 |

| Table 47: | Physical Interface Register Offsets           | . 286 |

| Table 48: | STOP_FAIL_EN and DROP_EN Setting              | . 303 |

| Table 49: | IDT-Specific Broadcast RapidIO Registers      | . 326 |

| Table 50: | IDT-Specific Non Broadcast Per-Port Registers | . 327 |

| Table 51: | IDT-Specific Per-Port Performance Registers   | . 351 |

| Table 52: | Serial Port Electrical Layer Registers        | . 382 |

| Table 53: | TX_LVL Values                                 | . 397 |

| Table 54: | AC JTAG level programmed by ACJT_LVL[4:0]     | . 399 |

| Table 55: | SerDes Register Map                           | . 446 |

| Table 56: | I <sup>2</sup> C Register Map                 | . 463 |

| Table 57: | Master Operation Sequence                     | . 472 |

| Table 58: | Special Characters and Encoding.              | . 533 |

| Table 50. | Control Symbol Construction                   | 534   |

## **About this Document**

This section discusses the following topics:

- "Scope" on page 19

- "Document Conventions" on page 19

- "Revision History" on page 20

### Scope

The *Tsi577 User Manual* discusses the features, capabilities, and configuration requirements for the Tsi577. It is intended for hardware and software engineers who are designing system interconnect applications with the device.

#### **Document Conventions**

This document uses the following conventions.

#### **Non-differential Signal Notation**

Non-differential signals are either active-low or active-high. An active-low signal has an active state of logic 0 (or the lower voltage level), and is denoted by a lowercase "\_b". An active-high signal has an active state of logic 1 (or the higher voltage level), and is not denoted by a special character. The following table illustrates the non-differential signal naming convention.

| State       | Single-line signal | Multi-line signal |

|-------------|--------------------|-------------------|

| Active low  | NAME_b             | NAME_b[3]         |

| Active high | NAME               | NAME[3]           |

#### **Differential Signal Notation**

Differential signals consist of pairs of complement positive and negative signals that are measured at the same time to determine a signal's active or inactive state (they are denoted by "\_p" and "\_n", respectively). The following table illustrates the differential signal naming convention.

| State    | Single-line signal       | Multi-line signal                |

|----------|--------------------------|----------------------------------|

| Inactive | NAME_p = 0<br>NAME_n = 1 | NAME_p[3] = 0<br>NAME_n[3] =1    |

| Active   | NAME_p = 1<br>NAME_n = 0 | NAME_p[3] is 1<br>NAME_n[3] is 0 |

20 About this Document

#### **Object Size Notation**

- A byte is an 8-bit object.

- A word is a 16-bit object.

- A doubleword (Dword) is a 32-bit object.

#### **Numeric Notation**

- Hexadecimal numbers are denoted by the prefix 0x (for example, 0x04).

- Binary numbers are denoted by the prefix 0b (for example, 0b010).

- Registers that have multiple iterations are denoted by {x..y} in their names; where x is first register and address, and y is the last register and address. For example, REG{0..1} indicates there are two versions of the register at different addresses: REG0 and REG1.

#### **Symbols**

This symbol indicates a basic design concept or information considered helpful.

This symbol indicates important configuration information or suggestions.

This symbol indicates procedures or operating levels that may result in misuse or damage to the device.

#### **Document Status Information**

- Preliminary Contains information about a product that is near production-ready, and is revised as required.

- Formal Contains information about a final, customer-ready product, and is available once the product is released to production.

## **Revision History**

#### **June 6, 2016, Formal**

- Updated "Reserved Register Addresses and Fields"

- Updated the second caution in "RapidIO Error Management Extension Registers"

- Updated the description of bit 31 (Reserved) in the following registers: "SRIO MAC x SerDes Configuration Channel 0", "SRIO MAC x SerDes Configuration Channel 1", "SRIO MAC x SerDes Configuration Channel 2", and "SRIO MAC x SerDes Configuration Channel 3"

- Removed Ordering Information from the manual. This information now resides solely in the *Tsi577 Hardware Manual*.

#### September 16, 2014, Formal

- Updated step 2 in the "Hot Extraction" procedure

- Added a new section, "Lane Sync Timer"

- Updated "Power-Down Options"

- Added Figure 14: Drive Strength and Equalization Waveform

- Added a new section, "Multicast Operation with Multiple Tsi57x Switches"

- Added a new section, "Maintaining Packet Flow"

- Updated steps 3 and 4 in "Control Symbol Example"

- Updated the description of Fatal Port Error in Table 22: Tsi577 Events

- Updated the description of "Per-Port Reset"

- Updated the description of "RIO Port x Error and Status CSR".PORT\_ERR

- Updated the definition of "Tsi577\_read\_prbs\_all.txt Script"

#### May 28, 2012, Formal

- Updated the second step in "Removing a Destination ID to Multicast Mask Association"

- Updated the second paragraph in "Payload"

- Updated "Port-writes and Multicast"

- Updated the registers listed in "Broadcast Registers to Program after Port Power Down"

- Added a note about how SW\_RST\_b is the only external indicator that a reset request has been received to "System Control of Resets" and Table 39

#### November 19, 2010, Formal

- Added more information about "Lookup Table Entry States"

- Added more information about "Port Aggregation: 1x and 4x Modes"

- Added a note to the "SRIO MAC x SerDes Configuration Global" register

- Added more information about "SRIO MAC x Digital Loopback and Clock Selection Register".DLT\_THRESH

#### August 2009, Formal

The have been no technical changes to this document. It has been updated to reflect IDT.

22 About this Document

## 1. Functional Overview

This chapter describes the main features and functions of the Tsi577. This chapter includes the following information:

- "Tsi577 Overview" on page 23

- "Serial RapidIO Interface" on page 28

- "Serial RapidIO Electrical Interface" on page 31

- "Multicast Engine" on page 29

- "Internal Switching Fabric (ISF)" on page 33

- "Internal Register Bus (AHB)" on page 33

- "I<sup>2</sup>C Interface" on page 34

- "JTAG Interface" on page 36

- "Port Numbering" on page 37

#### 1.1 Tsi577 Overview

The IDT Tsi577<sup>TM</sup> is IDT's fifth-generation RapidIO switch. Supporting 40 Gbps aggregate non blocking bandwidth at lower power than previous generation RapidIO switches.

Using the Tsi577, flexible port configurations can be selected through multiple port width and speed options. The Tsi577 can be configured as a 16-port 1x mode switch or a 4-port 4x mode switch (or various combinations of 1x and 4x modes). Each port on the device can be a single 4x mode port or four 1x mode ports and can operate at 1.25 Gbaud, 2.5 Gbaud, or 3.125 Gbaud (or any speed in between, on a quad grouping basis).

The Tsi577 contains all the benefits of the previous RapidIO switch generations, including:

- Industry best Multicast performance

- Traffic management through scheduling algorithms

- Programmable buffer depth

- Fabric performance monitoring to supervise and manage traffic flow

- Reduced number of clocks

- Low short and long reach power

- Industry best signal integrity

- 110 ns cut through latency

(4x or 1x 4x or 1x Multicast SP14 (1x)(1x)(1x) Enhanced Intenal Switching Fabric (1x)SP11 (1x) Registers (1x)JTAG IEEE1149.6 Boundary Scan Master and Slave Devices

Figure 1: Tsi577 Block Diagram

#### 1.1.1 Typical Applications

The Tsi577 can be used in many embedded communication applications. It is designed for systems with chip-to-chip DSP and processor aggregation, and connecting to network/backplanes.

The Tsi577 provides traffic aggregation through packet prioritization when it is used with RapidIO-enabled I/O devices. When it is in a system with multiple RapidIO-enabled processors it provides high performance peer-to-peer communication through its non-blocking switch fabric.

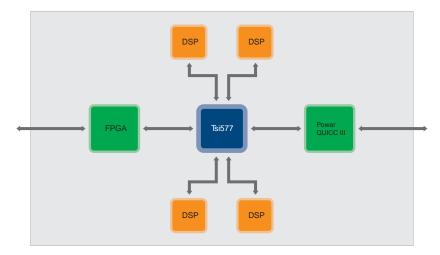

In wireless baseband, the Tsi577 provides a local interconnect between DSPs used for chip rate processing assist and symbol rate processing. This provides a scalable architecture to support more subscribers per card.

Figure 2: Wireless Baseband Card

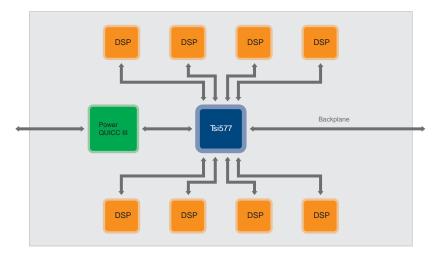

In video infrastructure cards, equipment vendors must maximize the number of DSPs per card to manage compression and decompression algorithms. These DSPs are controlled by a local processor and all these components are linked together by a low power, small form factor, low latency, multicast enabled Tsi577.

Figure 3: Video Infrastructure Card

#### 1.1.2 Features

The Tsi577 contains the following features:

#### Electrical Layer Serial RapidIO Features

- Up to 8 ports in 4x Serial mode

- Up to 16 ports in 1x Serial mode (each 4x port can be configured independently as four 1x ports)

- Operating baud rate per data lane: 1.25 Gbit/s, 2.5 Gbit/s, or 3.125 Gbit/s

- Full duplex bandwidth:

- 12.5 Gbit/s inbound and 12.5 Gbit/s outbound bandwidth at 3.125 GHz for a port configured for 4x mode<sup>1</sup>

- 3.125 Gbit/s inbound and 3.125 Gbit/s outbound bandwidth at 3.125 GHz for a port configured for 1x mode<sup>2</sup>

- Programmable serial transmit current with pre-emphasis equalization

- Loopback support for system testing

- Hot-insertion capable I/Os and hardware support

- Per-port power down modes to reduce power consumption

- Ability to reverse the bit ordering of a 4x port to simplify PCB layout

#### Transport Layer RapidIO Features

- Dedicated destination ID lookup table per port, used to direct packets through the switch

- Supports both hierarchical lookup tables and flat mode lookup tables (512 destination IDs per lookup table)

- Supports an optional, unique hierarchical destination ID lookup table covering all 64K possible destinations ID

- Low-latency forwarding of the Multicast-Event control symbol

- Error management capability

- Performance monitoring capability

- Reset-system interrupt support

- Debug packet generation in debug mode

#### Multicast Engine Features

- One multicast engine provides dedicated multicast resources without impacting throughput on the ports

- Eight multicast groups

- Sustained multicast output bandwidth, up to 10 Gbit/s per egress port

<sup>1.</sup> Usable data rate is 10 Gbit/s rather than 12.5 Gbit/s due to 8B/10B physical layer encoding.

<sup>2.</sup> Usable data rate is 2.5 Gbit/s rather than 3.125 Gbit/s due to 8B/10B physical layer encoding.

- 10 Gbit/s of instantaneous multicast input bandwidth<sup>1</sup>

- Packets are replicated to each egress port in parallel

- The multicast engine can accept bursts of traffic with different packet sizes

- Arbitration at the egress port to allow management of resource contention between multicast or non-multicast traffic.

System behavior when multicasting of packets which require responses is not defined in the *RapidIO Interconnect Specification (Revision 1.3) - Part 11 Multicast Specification*.

#### Other Device Interfaces

- Master and Slave mode I<sup>2</sup>C port, supports up to 8 EEPROMs

- Optionally loads default configuration from ROMs during boot-up, through I<sup>2</sup>C

- Ability to read and write EEPROMs through I<sup>2</sup>C during system operation

- IEEE 1149.1 and 1149.6 boundary scan, with register access

#### Internal switching fabric (ISF)

- Full-duplex, line rate, non-blocking switching fabric

- Prevents head-of-line blocking on each port

- · Eight packet buffers per ingress port

- Eight packet buffers per egress port

#### Register Access

- Registers can be accessed from any RapidIO interface and both the JTAG interface and I<sup>2</sup>C

- Optionally loads default configuration from ROMs during boot-up, through I<sup>2</sup>C

- Supports one outstanding maintenance transaction per interface

- Supports 32-bit wide (4 byte) register access

<sup>1.</sup> All bandwidths assume the internal switching fabric is clocked at  $156.25\ MHz$ .

## 1.2 Serial RapidIO Interface

The Tsi577 provides high-performance serial RapidIO interfaces that are used to provide connectivity for control plane and data plane applications. All RapidIO interfaces are compliant with the *RapidIO Interconnect Specification (Revision 1.3)*.

This section describes the transport layer features common to all Tsi577 RapidIO interfaces. The RapidIO interface has the following capabilities:

- RapidIO packet and control symbol transmission

- RapidIO packet and control symbol reception

- Register access through RapidIO maintenance requests

#### 1.2.1 Features

The following features are supported:

- Up to four 4x-mode or up to sixteen 1x-mode serial RapidIO ports operating at up to 3.125 Gbits/s

- Per-port destination ID look-up table, used to direct packets through the switch

This is a IDT-specific implementation. The *RapidIO Interconnect Specification (Revision 1.3)* standard implementation of look-up tables is also supported.

- RapidIO error management extensions described in RapidIO Interconnect Specification (Revision 1.3) Part 8, including both hardware and software error recovery

- · Low latency forwarding of the multicast control symbol

- Proprietary registers for performance monitoring and tuning

- Both cut-through and store-and-forward modes for performance tuning

- Debug packet generation and capture

- Multicast functionality, described in RapidIO Interconnect Specification (Revision 1.3) Part 11

- Head-of-Line blocking avoidance

#### 1.2.2 Transaction Flow Overview

Packets and control symbols are received by the Serial RapidIO Electrical Interface (Serial MAC) and forwarded to the RapidIO Interface (for more information on the Serial MAC, refer to "Serial RapidIO Electrical Interface" on page 71). Received packets have their integrity verified by error checking. Once the packet's integrity has been verified, the destination ID of the packet is used to access the routing lookup table to determine which port the packet should be forwarded to and whether the packet is a multicast packet. The packet is then buffered by the Internal Switch Fabric (ISF) for transmission to the port. After the packet is transferred to the egress port, the port transmits the packet. If a packet fails the CRC check, the packet is discarded and the transmitter is instructed to retransmit the packet through the use of control symbols.

The egress port receives packets to be transmitted from the ISF. The integrity of packets forwarded through the ISF is retained by sending the CRC code received with the packet. For more information on the input and ouput queues, refer to "Packet Queuing" on page 101.

The packet transmitter and the packet receiver cooperate to ensure that packets are never dropped (lost). A transmitter must retain a packet in its buffers until the port receives a packet accepted control symbol from the other end of the link.

#### 1.2.3 Maintenance Requests

A maintenance packet is the only packet type that will be modified by the switch. If the hop count value of the maintenance request is 0, the maintenance request is forwarded to the register bus for processing. The register bus accesses the registers in the appropriate port. The response to the maintenance request is compiled into a maintenance response packet and queued by the port for transmission. Maintenance packets with a non-zero hop count value have their hop count decremented, CRC recomputed, and are then forwarded to the port selected by the destination ID value in the look up table.

#### 1.2.4 Control Symbols

Control symbols received by the Tsi577 have their CRC validated, and their field values checked. If either the CRC is incorrect or the control symbol field values are incorrect, a packet-not-accepted control symbol is sent back and the control symbol is discarded. Otherwise, the control symbol is used by the port for purposes of packet management in the transmit port or link maintenance.

## 1.3 Multicast Engine

The Tsi577 multicast functionality is compliant to the *RapidIO Version 1.3 Part 11 Multicast Specification*.

#### 1.3.1 Multicast Operation

In a multicast operation, packets are received at the speed of any ingress port and broadcast at the speed of the egress ports to multiple ports capable of accepting packets for transmission.

Packets are routed to the multicast engine based on their destinationID and Transaction Type (TT) field value. If no match is found for the destinationID and TT field, then the ingress lookup tables are used to route the packet. A maximum of eight different DestID/TT field combinations can be routed to the multicast engine. Each destinationID/TT set can be multicast to a different set of egress ports. A set of egress ports that packets are multicast to is called a multicast group and is represented by the multicast mask in the group table. A multicast packet is never sent out on the port that it was received on. Any number of ports can share the same multicast group.

Multicast packets are accepted by egress ports based on priority. In the event that multicast and unicast traffic are competing for resources in the egress port, multicast specific egress arbitration can be used to favour multicast or unicast traffic. This allows a group of endpoints that need to multicast to each other to share the same multicast mask.

#### 1.3.2 Features

The Tsi577 supports multicast packet replication in accordance with *RapidIO Specification Version* 1.3, Part 11 Multicast.

The Tsi577 includes the following features:

- One multicast engine provides dedicated multicast resources without impacting throughput on the ports

- Eight multicast groups

- Packets are replicated to each egress port in parallel

- The multicast engine can accept bursts of traffic with different packet sizes

- Arbitration at the egress port to allow management of resource contention between multicast or unicast traffic

System behavior for the multicasting of packets which require responses is not defined in the *RapidIO Interconnect Specification (Revision 1.3) - Part 11 Multicast Specification.*

## 1.4 Serial RapidIO Electrical Interface

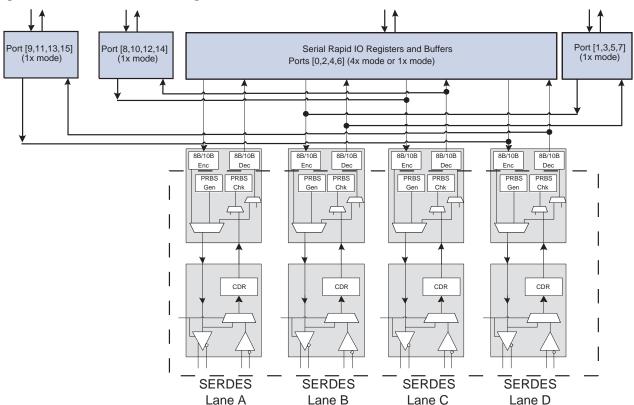

The Tsi577 has four 4x/1x Media Access Controllers (MAC). Each MAC contains four Serial RapidIO ports. Each of the MAC SRIO ports share four differential transmit lanes and four differential receive lanes.

Each of the MACs can operate in either 4x or 1x mode. Table 1 lists the associated Serial RapidIO (SRIO) Port number with each of the 4X/1X MACs.

Table 1: Tsi577 MAC Serial RapidIO Port Assignment

| MAC   | Port Number | Mode  | SERDES Lanes              |

|-------|-------------|-------|---------------------------|

| MAC 0 | SP0         | 4X/1X | 4X (A, B, C, D)<br>1X (A) |

|       | SP1         | 1X    | В                         |

|       | SP8         | 1X    | С                         |

|       | SP9         | 1X    | D                         |

| MAC 2 | SP2         | 4X/1X | 4X (A, B, C, D)<br>1X (A) |

|       | SP3         | 1X    | В                         |

|       | SP10        | 1X    | С                         |

|       | SP11        | 1X    | D                         |

| MAC 4 | SP4         | 4X/1X | 4X (A, B, C, D)<br>1X (A) |

|       | SP5         | 1X    | В                         |

|       | SP12        | 1X    | С                         |

|       | SP13        | 1X    | D                         |

| MAC 6 | SP6         | 4X/1X | 4X (A, B, C, D)<br>1X (A) |

|       | SP7         | 1X    | В                         |

|       | SP14        | 1X    | С                         |

|       | SP15        | 1X    | D                         |